#### BUS SCHEDULING IMPLEMENTATION ON THE CELL PROCESSOR

#### BY

#### DEEPTI KUMAR CHIVUKULA

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2010

Urbana, Illinois

Adviser:

Associate Professor Marco Caccamo

# **ABSTRACT**

Real-time computing is the study of hardware and software systems that are subject to a "real-time constraint" - i.e., strict deadline guarantees. With uncontrollable cache and front side bus, in the modern computer architectures, the estimation of a tight bound, worst case execution time (WCET) is difficult. The new generation computer architecture, Cell Broadband Engine Architecture (CBEA), has a software controlled front side bus (i.e. Element Interconnect Bus) that helps moderate the unpredictable task execution time problem. The CBEA is a heterogeneous chip system containing one Power Processing Element (PPE) and eight Synergistic Processing Elements (SPEs), each having an internal independent local storage memory.

In this thesis, using CBEA as a platform, I implemented an interrupt based scheduling framework that uses Element Interconnect Bus (EIB) in a temporally predictable manner. The framework is built by abstracting away low-level architectural features. Experiments were also performed to show that the real-time transactions of feasible transaction sets are executed before deadline when scheduled according to a real-time scheduling algorithm, while the same transactions can miss their deadlines when scheduled according to an arbitrary (non-real-time) scheduling policy.

To my husband Sujan, for his love, motivation and support

# **ACKNOWLEDGMENTS**

First and foremost, I would like to thank my adviser, Dr. Marco Caccamo, who has been more than just an academic and research adviser over the last two years. He has been a mentor and a valuable guide, giving me complete freedom to choose a problem that I am really excited about, and thus made my research experience fantastic.

For their advice, inspiration, insights and discussions, I would like to thank other professors and fellow graduate students in the Beckman Institute and Siebel Center, including Dr. Narendra Ahuja, Dr. Lui R. Sha, Rodolfo Pellizzoni and Bach D. Bui.

I would also like to thank Shakti Kapoor, Senior Technical Staff Member at IBM Austin, for his timely support in terms of connecting me to the right people to talk.

Thanks are also due to my close friends: Manoj, Ramya, Sreekanth, Siva Kumar Sastry Hari, and many more for making my life at UIUC so enjoyable.

Finally, I would like to thank my parents for their love, encouragement and support.

# TABLE OF CONTENTS

| LIST OF TABLES                                                                                                               | 'ii                              |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LIST OF FIGURES                                                                                                              | ii                               |

|                                                                                                                              | 1<br>5                           |

| <ul><li>2.1 The Three Walls</li></ul>                                                                                        | 6<br>7<br>9<br>5                 |

| 3.1 Partitioning of the Applications                                                                                         | 6<br>8<br>24<br>32               |

| 4.1 Terms and Terminology                                                                                                    | 33<br>34<br>37<br>40<br>36       |

| 5.1Scheduling Framework: PPE Side55.2Scheduling Framework: SPE Side65.3Development Structure65.4Flow of Implementation Code6 | 57<br>58<br>54<br>58<br>58<br>70 |

| CHAPT  | ER 6 EXPERIMENTAL RESULTS, CONCLUSION AND FU- |

|--------|-----------------------------------------------|

| TUR    | E WORK                                        |

| 6.1    | Experimental Setup                            |

| 6.2    | Experimental Results                          |

| 6.3    | Conclusion                                    |

| 6.4    | Future Work                                   |

| APPENI | DIX A IMPLEMENTATION CODE AND BIT ORDERING    |

| IN C   | ELL PROCESSOR                                 |

| A.1    | PPU: simple.c                                 |

| A.2    | PPU: cFile.c                                  |

| A.3    | PPU: Makefile                                 |

| A.4    | SPU: simple_spu.c                             |

| A.5    | SPU: Makefile                                 |

| A.6    | SPU: barrier_heavy.h                          |

| A.7    | SPU: spu_slih_reg.c                           |

| A.8    | SPU: spu_slih_reg.h                           |

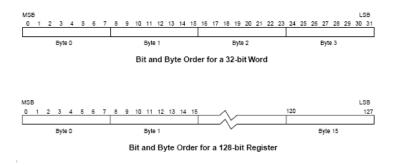

| A.9    | Bit Ordering and Numbering                    |

| REFERI | ENCES                                         |

# LIST OF TABLES

| 3.1 | Values of Behavior    | 28 |

|-----|-----------------------|----|

| 5.1 | Schedule Table        | 70 |

| 6.1 | DMA Transmission Time | 72 |

# LIST OF FIGURES

| 2.1 | The Cell Broadband Engine 6                                |

|-----|------------------------------------------------------------|

| 2.2 | SPE Architectural Block Diagram                            |

| 2.3 | Memory Flow Controller                                     |

| 2.4 | CBEA: Element Interconnect Bus                             |

| 2.5 | Sending Phase                                              |

| 2.6 | Command Phase                                              |

| 2.7 | Data Phase                                                 |

| 2.8 | Receiving Phase                                            |

| 3.1 | Application Partitioning Models                            |

| 3.2 | PPE-Centric Models: Multistage Pipeline Model and Parallel |

|     | Stages Model                                               |

| 3.3 | PPE-Centric Service Model                                  |

| 3.4 | The Cell Storage Domains                                   |

| 4.1 | Types of Transactions                                      |

| 4.2 | Overlap Contention                                         |

| 4.3 | Overload Contention                                        |

| 4.4 | Non-circular Transaction Set                               |

| 4.5 | Circular Transaction Set                                   |

| 4.6 | Indexed Straight Line Representation                       |

| 4.7 | An Example of the POBase Algorithm                         |

| 4.8 | Scheduling Intervals on the Execution Timeline             |

| 4.9 | Constructed Graph G                                        |

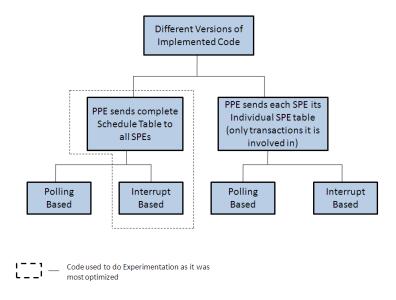

| 5.1 | Different Versions of Implemented Code                     |

| 5.2 | Flow of Implementation Code 69                             |

| 5.3 | Snapshot of User Interface                                 |

| 6.1 | Experimental Transaction Set                               |

| A.1 | Big Endian Ordering                                        |

# CHAPTER 1

# INTRODUCTION

A real-time system can be a hardware or a software system, whose application is considered to be *mission critical*. The total correctness of an operation, for such a system, depends not only on its logical correctness but also upon the time in which it is performed. In fact, the classical concept states that in a "hard" real-time system, the completion of an operation after its deadline is considered to be useless. Thus, real-time systems are used when there is a need for the deadlines of all the tasks to be guaranteed: to analyze the temporal behavior of the system, the worst case execution times (WCET) must be reliably estimated. Examples of such hard real-time systems include car engine systems, avionics systems, medical systems (like heart pacemakers) and industrial process controllers.

A significant source of randomness in estimating WCET lies in the *uncontrollability* of interconnection architectures, specifically both shared cache and front side bus (FSB). These architectures are used by CPU and direct memory access (DMA)-enabled peripherals to communicate amongst each other and with the main memory.

This problem, of randomness in estimating WCET, is potentially more severe in multiprocessor systems with a multitasking operating system (OS), as they have more entities which are concurrently competing for bus access. In such a system, execution time of a task can be unexpectedly extended by the execution of other tasks or DMA-enabled peripherals. The authors of [1] observed that extensions in execution time may be as high as 44%.

There have been significant research efforts on interconnection architectures for multi-core processors which have features suited for real-time systems, especially in the field of networks-on-chip (NOC). These works have been surveyed earlier in [2]. Commercial multi-core processors with software-controlled interconnections have also been developed, such as the IBM Cell Broadband Engine Architecture (CBEA) which is well distinguished for its high performance.

The main research issue is to how to provide software designers with: (1) a

practical and accurate abstraction of the real scheduling problem on multiprocessor bus and (2) an effective scheduling methodology that optimizes multiprocessor bus utilization. The present research focuses on addressing this problem on a specific multiprocessor bus architecture, specifically CBEA.

CBEA [3] is a new architecture that extends the 64-bit PowerPC Architecture. It is the result of collaboration between Sony, Toshiba and IBM, popularly known as STI, which was formally started in early 2001. It consists of nine processing elements, including an IBM 64-bit Power Architecture core called the Power Processing Element (PPE), augmented with eight co-processors called Synergistic Processor Elements (SPE) which contain private 256 kB of local storage (LS). All processing units and peripherals communicate with the main memory and other units through the Element Interconnect Bus (EIB) [4], which acts like an FSB. The EIB supports multiple transactions at the same time and its accesses are software controllable. It provides more control for moving or accessing memory data of the processing elements. Also, it provides more control over the cache usage, thus making this architecture intrinsically more predictable. Due to its hardware features, CBEA overcomes three important limitations of modern microprocessor performance - power use, memory use and processor frequency.

Support provided by the unique software features of CBEA also enhances control over EIB and the cache. Some of these features include dedicated instruction sets for each type of processor (PPE and SPEs), flexibility in developing applications in either C/C++/assembly language, good application programming interface (API) support called software development kit (SDK), and enhanced ability for parallelization (PPE and SPE Linux threads). These features are discussed in Chapter 3.

As mentioned earlier, our research group focused on developing an abstraction of the scheduling problem as well as an effective scheduling methodology that predictably schedule the multiprocessor bus. My key contribution to this effort, which is the focus of this thesis, was to build a framework that would allow the team to implement and test the performance of a class of scheduling algorithms for CBEA, while maintaining high throughput. The motivation for building the framework is that CBE's low level arbitration is complex and analyzing how requests compete for access to the bus is not easy. This framework would abstract away from the user the low level physical bus implementation. Further, it would allow table based scheduling through which we can eliminate all contentions for access to the bus and make it completely predictable. A key consideration while

building the framework was to ensure that it is simple to understand and be used by developers.

I have also conducted experiments to show that the real-time transactions of feasible transaction sets are executed before deadline when executed according to the real-time scheduling algorithm, while the same transactions can miss the deadlines if my scheduling framework is not used.

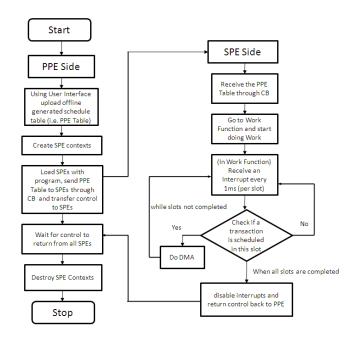

The implemented framework is interrupt based: it receives a timer interrupt at the beginning of each time slot (or quanta), and it makes a scheduling decision for the current slot based on a table that is generated offline by a real-time scheduling algorithm. The framework abstracts away from the low-level physical bus implementation, which includes the data and command arbiter. If a transaction is scheduled in a slot, a DMA packet, of the transaction of a given size, will be transferred from source to destination in that slot through EIB. The size of a DMA packet to be transferred is decided on the basis of bus bandwidth and slot size. The source and destination of DMA packets are SPE units on the chip. Each SPE receives data specific to the transactions it is involved in. The interrupt mechanism is implemented on SPEs, and interrupts are fired periodically depending on the timer value.

Many hardware and software hurdles (Chapters 2 and 3) had to be overcome to successfully run offline generated schedules on the implemented framework. This merits a more detailed discussion covering the unique challenges that were faced during the project.

In terms of hardware, design of EIB as well as its arbiter in CBEA is inherently complex. Thus, during the implementation of the framework I faced several challenges including incorporating multiple degrees of parallelism on the EIB, eliminating initial delay in the first phase of task execution, avoiding delays caused by the cell arbiter as well as incorporating alignment restrictions imposed by DMA. These are explained in more detail below.

The EIB comprises a 4-ring structure (2 clockwise and 2 anticlockwise directions) and has multiple degrees of parallelism: each bus ring can carry up to three concurrent transactions. The bus ring can start a new task after every three cycles, which causes an initial delay in the first phase of the task execution. Details about the different phases of a task on the EIB are covered in Chapter 2. Tasks on the bus can delay each other further if they share the same bus segment. Details of the types of contentions on EIB and how they affect the task execution time are described in Chapter 4.

Central arbiter is responsible for handling the individual data transactions and scheduling them so that they move around the ring and eventually end up on their respective destination units. The data arbiter implements round-robin bus arbitration with two levels of priority - memory interface controller (interface between the main memory and the EIB) has the highest priority and the rest of the units on the chip have a lower priority. The data flows on the EIB in a stepwise manner around the ring. The data arbiter does not allow a data transaction to be transferred along hops if its path is more than half the ring diameter. That is, a data ring is granted to a requester only so long as the circuit path requested is not more than six hops in either direction. An important design consideration was that if the request is greater than six hops, the requester must wait until a data ring operating in the opposite direction becomes free.

Another important hardware challenge was the alignment restrictions imposed by DMA. Non-aligned DMAs (not at 16-byte boundary) are not supported by CBEA. If non-aligned DMA operation is encountered, the MFC command queue processing is suspended and DMA alignment interrupt is generated. Resolving these exceptions takes up a lot of processor time which again causes delays in the execution of tasks on the bus. DMA accesses in the main storage domain are atomic (128-bit) if they meet the requirements of the PowerPC architecture. All other DMA transfers, if greater than a quadword (16-byte) or non-aligned, are performed as a set of smaller (1, 2, 4 and 8 bytes), disjointed atomic accesses. The number and alignment of these accesses are implementation dependent. Further details of the alignment issues have been illustrated in Chapter 3.

There were some hurdles during software implementation as well. My framework was implemented using a PPE-centric type of model called the parallel stage model, as discussed in Chapter 3. The parallel stage model executes different portions of data in parallel by dividing data among different processing elements (SPEs) - the PPE creates software threads (the types of software threads that run on PPE and SPEs are explained in Chapter 3) and puts them on SPEs which execute the data in parallel. Thus, the main issue was to locate exploitable concurrency in a task to successfully divide the data for parallel computation. Other challenges faced while trying to parallelize the data computation were data dependencies and overhead in synchronizing concurrent memory accesses or transferring data between different processor elements (SPEs).

All the above mentioned problems were resolved and I was also able to leverage the low level features of EIB and central arbiter to successfully implement the

described framework. More details on the implementation are provided in later chapters.

# 1.1 Thesis Organization

This thesis is divided into two main parts. Before describing the framework implementation, it is critical to have a good understanding of CBEA. Thus, in Part 1 of the thesis, I describe the architecture and various software features in detail. Chapter 2 provides an overview of the architecture of CBE. Chapter 3 covers the programming process on PPE and SPEs of the CBE.

Part 2 of the thesis deals with actual implementation of the framework and experimental results. Chapter 4 begins with description of the bus model and explanation of the terminology that will be used in Chapter 5. This chapter also provides a brief overview of a novel dynamic scheduling algorithm: it is important background material needed to understand the scope of the framework and my experimentation work. Chapter 5 explains the actual implementation of the proposed framework. Chapter 6 describes results of the experiments that were conducted, concluding remarks as well as details of future work.

# CHAPTER 2

# CELL BROADBAND ENGINE ARCHITECTURE

First generation Cell Broadband Engine (CellBE) is the first incarnation of a new family of microprocessors, called *Cell Broadband Engine Architeciture* (CBEA), that extends the 64-bit PowerPC Architecture. CBEA is the result of collaboration between Sony, Toshiba, and IBM, known as STI, formally started in early 2001.

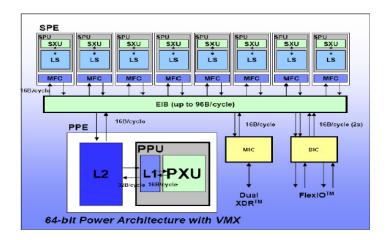

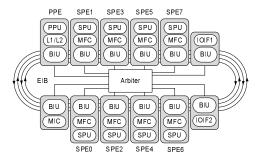

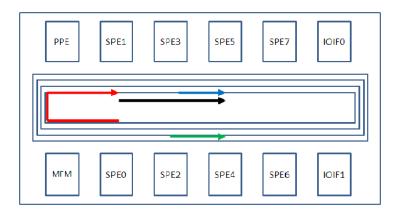

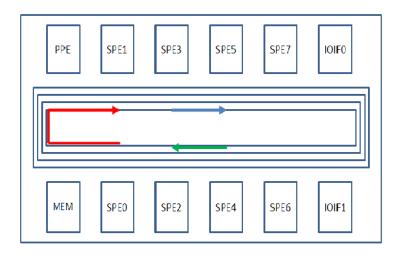

CBEA, as shown in Figure 2.1, consists of 12 core components connected through the Element Interconnect Bus (EIB): One Power Processing Element (PPE), eight Synergistic Processing Elements (SPEs), one Memory Interface Control Unit (MIC), and two I/O Interface Control Units (IOIF0 and IOIF1).

PPE is more adept at control-intensive tasks and is quicker at task-switching. SPEs are more adept at compute-intensive tasks and are slower at task switching. While either processor is capable of doing both types of tasks, this specialization has increased the efficiency in implementation of both PPE and, especially, SPEs. It is a significant factor in improving CBE's peak computational performance, area and power efficiency, by an order of magnitude (approximately) over conventional PC processors.

Figure 2.1: The Cell Broadband Engine

This chapter is organized in three sections. Sections 2.1 talks about the limita-

tions of modern microprocessors and how CBEA overcame these hurdles. Section 2.2 talks about the various hardware features of CBEA including Power Processor Element (PPE), Synergistic Processor Elements (SPEs), Memory Interface Controller (MIC), Element Interconnect Bus (EIB) and Cell Broadband Engine Interface (BEI).

#### 2.1 The Three Walls

As mentioned earlier, CBE overcomes three important limitations of modern microprocessor performance: power use, memory use and processor frequency. Following is a detailed description of how CBEA overcomes these hurdles.

#### 2.1.1 Power Wall

Microprocessor performance is often limited by achievable power dissipation, rather than by number of available integrated circuit resources (transistors and wires). Thus, power efficiency has to be improved to significantly increase microprocessor performance. One way to increase power efficiency is to differentiate between processors optimized to run an operating system and control-intensive code, and processors optimized to run compute-intensive applications.

CBE achieves this by providing a general purpose PPE to run the operating system and other control-plane code, and eight SPEs specialized for computing data-rich (data-plane) applications.

# 2.1.2 Memory Wall

Latency to DRAM memory for multi-gigahertz symmetric multiprocessors, even those with integrated memory controllers, is currently approaching 1,000 cycles. As a result, program performance is dominated by the activity of moving data between main storage (effective-address space that includes main memory) and the processor. Compilers and even application writers must increasingly manage this movement of data explicitly, even though hardware cache mechanisms are supposed to relieve them of this task.

CBE's SPEs use two mechanisms to deal with long main-memory latencies: (a) 3-level memory structure (main storage, local storages in each SPE, and large register files in each SPE) and (b) asynchronous DMA transfers between main and local storage. These features allow programmers to schedule simultaneous data and code transfers to cover long latencies effectively. As a result, CBE can usually support 128 simultaneous transfers between the eight SPE local storage and main storage. This surpasses the number of simultaneous transfers on conventional processors by a factor of almost 20.

#### 2.1.3 Frequency Wall

Conventional processors require increasingly deeper instruction pipelines to achieve higher operating frequencies. This technique has reached a point of diminishing returns - and even negative returns if power is taken into account.

CBEA, on which the CBE is based, allows both PPE and SPEs to be designed for high frequency without excessive overhead. PPE achieves efficiency primarily by executing two threads simultaneously, rather than by optimizing single-thread performance. Each SPE achieves efficiency by using a large register file, which supports many simultaneous in-flight instructions without the overhead of register-renaming or out-of-order processing. Each SPE also achieves efficiency by using asynchronous DMA transfers, which support many concurrent memory operations without overhead of speculation.

#### 2.1.4 Cell's Solution

CBE takes care of problems posed by power, memory and frequency limitations, by individually optimizing control-plane and data-plane processors. As a result a processor, with the power budget of a conventional PC processor, can theoretically be expected to provide an approximately ten-fold improvement in peak performance compared to a conventional processor.

Of course, actual application performance varies. Some applications may benefit little from SPEs, while others show a performance increase well in excess of ten-fold. In general, compute-intensive applications that use 32-bit or smaller data formats (such as single-precision floating-point and integer) are excellent candidates for the CBE.

## 2.2 Architectural Overview of CBEA

In the following sections, we provide architectural features and the hardware environment of the CBEA.

#### 2.2.1 PowerPC Processor Element (PPE)

PPE is the main processor that contains a 64-bit PowerPC Architecture reduced instruction set computer (RISC) core with a traditional virtual memory subsystem. It consists of two main units, the Power Processor Unit (PPU) and the Power Processor Storage Subsystem (PPSS).

PPE performs multiple functions, like running the operating system, managing system resources, as well as control processing, including the allocation and management of SPE threads. It can run legacy PowerPC Architecture software and performs well executing system-control code. It supports both the PowerPC instruction set and the Vector/SIMD Multimedia Extension instruction set.

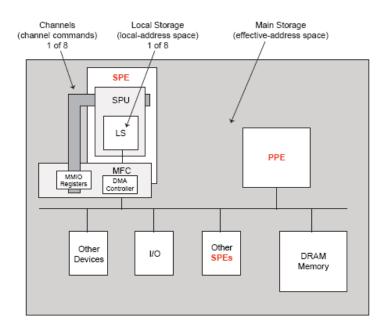

## 2.2.2 Synergistic Processor Elements (SPEs)

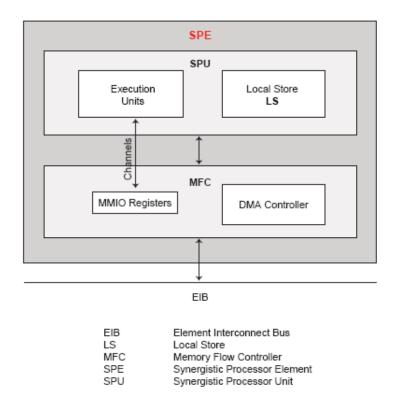

CBE includes eight SPEs that are SIMD processors optimized for data-rich operations which are allocated to them by the PPE. Each of these identical elements contains a RISC core, 256 kB, software-controlled local storage (LS) for instructions and data, and a large (128-bit, 128-entry) unified register file. It consists of two main units (shown in Figure 2.2), the Synergistic Processor Unit (SPU) and the Memory Flow Controller (MFC). Also, each SPE has full access to coherent shared memory, including the memory-mapped I/O space.

SPEs support a special SIMD instruction set, and they rely on asynchronous DMA transfers to move data and instructions between main storage (the effective-address space that includes main memory) and their local storages (LSs). SPE DMA transfers access main storage using PowerPC effective addresses. As on the PPE, address translation is governed by PowerPC Architecture segment and page tables. An SPE is a 128-bit processing unit that has a Memory Flow Control (MFC) unit which controls the memory management unit and the DMA engine. The method considered in this work for moving data between LSs, and between system memory and LSs, is DMA. A software designer operates the DMA engines by issuing commands to its MFC. The command must specify the starting and the

ending addresses of the transaction and its size. Each SPE contains a bus interface unit (BIU) that provides an interface from the SPE to EIB.

SPE is optimized for running compute-intensive applications, and not for running the operating systems. The name *synergistic* for this processor was chosen carefully because there is a mutual dependence between PPE and the SPEs. The latter depend on the former to run the operating system and, in many cases, the top-level control thread of an application. On the other hand, PPE depends on SPEs to provide the bulk of the application performance.

Figure 2.2: SPE Architectural Block Diagram

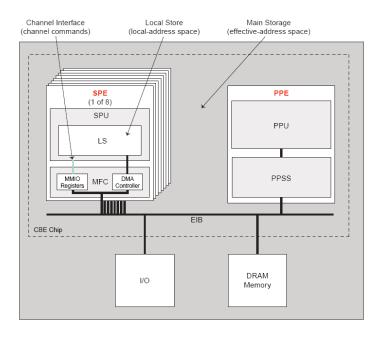

## 2.2.3 Memory Flow Controller

As shown in Figure 2.3, each SPU has its own Memory Flow Controller (MFC) that serves as the SPU's interface to main storage, other processor elements and system devices. MFC's primary role is to interface its LS storage domain with the main-storage domain. It does this by means of a DMA controller that moves instructions and data between its LS and main storage. MFC also supports other functions, including storage protection on the main storage side of its DMA trans-

fers, synchronization between main storage and the LS, as well as the communication functions (such as mailbox and signal-notification messaging) with PPE, other SPEs and devices.

In my thesis I will focus on only DMA transfers and mailboxes since I used these two mechanisms in implementing my framework.

Figure 2.3: Memory Flow Controller

# 2.2.4 Memory Interface Controller (MIC)

MIC provides the interface between Element Interconnect Bus (EIB) and main storage. It supports two Rambus Extreme Data Rate (XDR) I/O (XIO) memory channels and memory accesses on each channel of 1 - 8, 16, 32, 64, or 128 bytes.

# 2.2.5 Element Interconnect Bus (EIB)

PPE and SPEs communicate coherently with each other, with main storage as well as with I/O through the EIB (see Figure 2.4). The bus includes a 16-byte wide 4-ring structure (two clockwise and two counterclockwise) for data transfer, a data and command arbiter, and a tree structure for commands.

Each participant on the EIB has one 16-byte read port and one 16-byte write port. The bus has multiple degrees of parallelism: each bus ring can carry up to three concurrent transactions. Data flows on an EIB channel stepwise around the ring. Since there are 12 participants or units, the total number of steps around the channel back to the point of origin is 12. Six steps is the longest distance between any pair of participants. An EIB channel is not permitted to convey data requiring more than six steps; such data must take the shorter route around the circle in the other direction. The number of steps involved in sending the packet has very little impact on transfer latency: clock speed driving the steps is very fast relative to other considerations. However, longer communication distances are detrimental to the overall performance of the EIB as they reduce available concurrency. The EIB's internal bandwidth is 96-bytes per cycle, and it can support more than 100 outstanding DMA memory requests between main storage and the SPEs.

Figure 2.4: CBEA: Element Interconnect Bus

The transfer of a transaction on the bus takes place in four steps or stages - send phase, command phase, data phase and receive phase. Each of these steps is detailed in the section below.

#### 2.2.5.1 Sending Phase

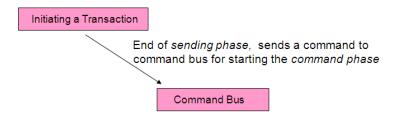

*Sending Phase*, shown in Figure 2.5, is responsible for initiating a transaction. It consists of all processor and DMA controller activities needed before transactions are injected into any components.

At the end of this phase, a command is issued to the command bus to begin the next phase.

Figure 2.5: Sending Phase

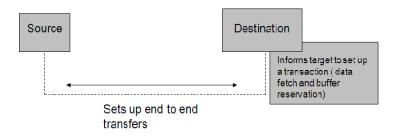

#### 2.2.5.2 Command Phase

Command Phase shown in Figure 2.6 coordinates end-to-end transfers across the EIB. This phase is also responsible for coherency checking, synchronization, and inter-element communication. EIB informs the read or write target element of the transaction in progress to allow the target to set up the transaction (i.e., data fetch or buffer reservation).

Figure 2.6: Command Phase

#### 2.2.5.3 Arbitration Phase

A low-level round robin scheduler arbitrates bus accesses between contending transactions stored in the post-command phase queue (arbitration phase together with data phase is called post-command phase). This phase occurs when the BIU has to wait for bus access due to the contention between atomic transactions on the bus.

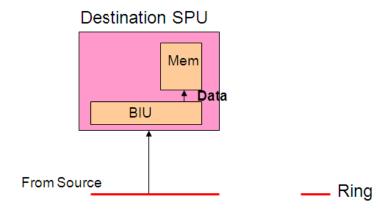

#### 2.2.5.4 Data Phase

As shown in Figure 2.7 *Data Phase* handles data ring arbitration and actual data transfers across the ring. This phase grants access to packets through one of the four data rings when a ring becomes free and ensures that no more than six

hops are needed along the ring. End-to-end transport of packets happens over a pipelined circuit-switched granted EIB Ring.

Figure 2.7: Data Phase

#### 2.2.5.5 Receiving Phase

Receiving Phase shown in Figure 2.8 concludes the transaction by transferring received data from the receiving node's BIU to its final destination at that receiver, such as local storage memory or the system memory.

Figure 2.8: Receiving Phase

# 2.2.6 Cell Broadband Engine Interface (BEI)

BEI manages data transfers between the EIB and I/O devices. It provides address translation, command processing, an internal interrupt controller, and bus interfacing. It supports two Rambus FlexIO external I/O channels. One channel supports only non-coherent I/O devices. The other channel can be configured to support

either non-coherent transfers or coherent transfers that extend the logical EIB to another compatible external device, such as another CBE.

# 2.3 Chapter Conclusion

In this chapter, I gave a brief overview of the CBE architecture, as well as the functions of each of its hardware components. As discussed earlier, the unique architecture of the CBE allows it to overcome serious limitations of modern microprocessors and deliver approximately ten-fold improvement in performance. In the next chapter I will describe unique and important architecture details, knowledge of which is required for programming on CBEA.

# **CHAPTER 3**

# PROGRAMMING ENVIRONMENT ON CBEA

Support provided by the unique software features of CBEA enhances our control over the interconnection architecture. Thus, it is important to understand the programming environment of CBEA to know the complexity involved in abstracting from the low level bus architectural constraints. This chapter gives an overview of programming on the nine processor elements of CBEA, i.e. PPE and eight SPEs. As already discussed in Chapter 2, PPE on the CBEA is optimized to run the operating system and any control-intensive code, while the SPEs are optimized to run compute-intensive applications. Running an application on these processors requires an understanding of how applications partition tasks among different processors as well as how these tasks are actually executed on them. For further reference a detailed description of the programming process is given in [5] and [6].

This chapter is organized in four sections. Partitioning of applications is described in Section 3.1. The next section deals with creation of threads; these are used to send processing requests to different processors. Section 3 describes instruction sets that are used to process these tasks. Finally in the last section, an overview of how SPEs and PPEs interact is provided.

# 3.1 Partitioning of the Applications

All applications running on the Cell Broadband Engine need to divide the work among the nine processors. The following considerations have to be taken into account while deciding on how to distribute the workload and data.

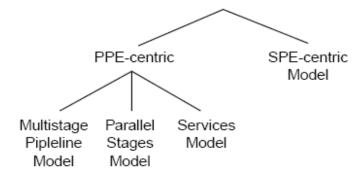

Program structure: Any application will usually have both compute intensive tasks as well as control intensive tasks. In CBEA, the two types of tasks are assigned to different types of processors. Thus, the choice of a task partitioning model, i.e. PPE-centric or SPE-centric as shown in

Figure 3.1, will depend on whether the application is more compute-intensive or more control intensive. The model choice ensures that the application is run optimally on the processors.

- Program data access and data flow patterns: After deciding the type of partitioning, the developer will determine if data is going to be sent in a parallel fashion or serially to SPEs, depending on the processor's coded functionality.

- Optimizing cost: Context switching can cause the processing time to increase substantially as SPEs have to be stopped while local storages are reloaded. Thus, the developer needs to be careful to write code to minimize context switching.

Our implementation used a PPE-centric model, which is described below. Details about the justification for using this model are given in Chapter 5.

Figure 3.1: Application Partitioning Models

#### 3.1.1 PPE-Centric Model

In this model, the main application runs on the PPE, and individual tasks are offloaded to the SPEs. PPE then waits for, and coordinates, the results returning from the SPEs. This model fits an application with serial as well as with parallel data computation.

The PPE-centric model can be classified into three sub-models depending on how SPEs are used:

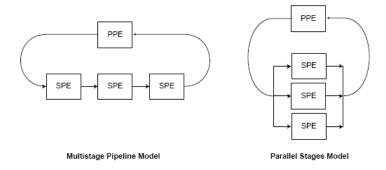

• Multistage pipeline model (shown on left of Figure 3.2): It is used when a task requires sequential stages, where the SPEs can act as a multi-stage

pipeline. Each SPE is responsible for one stage of the process. This model is not suitable for parallel processing owing to difficulty in load balancing. Additionally, this model increases the costs due to greater data movement.

- Parallel stage model (shown on right of Figure 3.2): Suitable when tasks involve a large amount of data that can be partitioned and executed in parallel.

Thus, each SPE is used to execute different portions of data simultaneously.

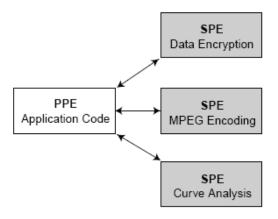

- Services model (shown in Figure 3.3): Here, PPE assigns different services

to different SPEs, and the PPE's main process calls upon the appropriate

SPE when a particular service is needed. For example one SPE processes

data encryption, another SPE processes MPEG encoding, and a third SPE

processes curve analysis. Fixed static allocation of SPE services should be

avoided. These services should be virtualized and managed on a demandinitiated basis.

We used the parallel stage model in our framework. More details for our choice of sub-model are presented in Chapter 5.

Figure 3.2: PPE-Centric Models: Multistage Pipeline Model and Parallel Stages Model

### 3.2 Threads on PPE and SPE

A software developer also needs to understand how applications are executed on CBEA. This will give the developer more control and he/she will be able to effectively abstract the low level design.

Figure 3.3: PPE-Centric Service Model

The architecture can support several types of operating systems. Our research group used the Linux operating system (Fedora Core 7), which was running on the Sony play station (PS)3.

Every program is a process to the operating system. A process is a task that competes for execution time on the microprocessor, and has resources. Linux allows a program to execute multiple threads of execution. One program can create independent threads, which share the resources of the parent process, but execute independently of each other, and the parent process. A thread running in the Linux OS environment is referred to as Linux thread.

In CBEA, the main thread of a program is a Linux thread running on the PPE. Any Linux thread running on a PPE is called a PPE thread. The main thread can spawn one or more CBE Linux tasks. A CBE Linux task has one or more Linux threads associated with it that may execute on either a PPE or an SPE. All Linux threads within the task share the tasks resources.

The operating system defines the mechanism and policy for scheduling an available SPE. It must prioritize among all the Cell Broadband Engine Linux applications in the system, and it must schedule SPE execution independent from regular Linux threads. It is also responsible for runtime loading, passing parameters to SPE programs, notification of SPE events and errors, and debugger support.

A thread running on SPE is called an SPE thread. It has its own SPE context which includes the 128x128-bit register file, program counter, and MFC command queues. Further, it can communicate with other execution units or with effective address memory through the MFC channel interface. All architectures create SPE threads; however, SPE architecture of CBEA is new and so it needs to create SPE

threads in a specific way. It is thus important to understand how to load, run and destroy threads on SPEs, which is described in the next section.

Additionally, programming on the CBE processor requires an understanding of parallel programming as it is a multi-core system. Section 3.2.2 reviews different styles of parallel programming on the CBE processor.

#### 3.2.1 SPE Thread Creation

Programs to be run on an SPE are often written in C or C++ (or assembly language) and can use the SPE data types and intrinsics defined in the SPU C/C++ Language Extensions. A PPE module starts running an SPE module by first creating a thread on the SPE. It creates SPE threads using the SPE context create, program load, context run, pthread join and context destroy library calls, all of which are provided in the SPE runtime management library except pthread join.

#### 3.2.1.1 Creating Threads

- flags This is a bit-wise OR of modifiers that is applied when the new context is created. A number of values are accepted for this parameter out of which we use SPE\_MAP\_PS Request permission for memory-mapped access to the SPE threads problem state area.

- gang It is a collection of contexts in which the context being created should be made a part of.

#### Loading the SPEs

- spe The SPE context in which the specified program is to be loaded.

- program Indicates the program to be loaded into the SPE context.

#### **Running the SPEs**

```

int spe_context_run(spe_context_ptr_t spe,

unsigned int *entry, unsigned int runflags,

void *argp, void *envp,

spe_stop_info_t *stopinfo)

```

- spe The SPE context to be run.

- entry Initial value of the instruction pointer in which the SPE program should start executing. Upon return from the spe\_context\_run call, the value pointed to by entry contains the next instruction to be executed upon resumption of the program.

- runflags This is a bit-wise OR of modifiers which request specific behavior when the SPE context is run. Flags include: - 0 - Default behavior. No modifiers are applied.

- argp An optional pointer to application specific data. It is passed as the second parameter of the SPU program.

- envp An optional pointer to environment specific data. It is passed as the third parameter of the SPU program.

- stopinfo An optional pointer to a structure of type spe\_stop\_info\_t that provides information as to the reason why the SPE stopped running.

#### **Destroy the SPE threads**

```

spe_context_destroy (spe_context_ptr_t spe)

```

Destroys the context for the SPE context *spe*. The SPE threads that were initially created are destroyed.

## 3.2.2 Parallel Programming

For efficient computation it is important to understand how tasks can be executed in parallel, on the eight SPEs. The key to parallel programming is to locate exploitable concurrency in a task. The basic steps for parallelizing any program are:

- Locate concurrency: Time spent analyzing the program, its algorithms and data structures will be repaid many-fold in the implementation and coding phase. The most important question that we need to ask ourselves is Will the anticipated speedup from parallelizing a program be greater than the effort to parallelize a program, which includes any overhead for synchronizing different tasks or access to shared data? Another question we can ask ourselves is Which parts of the program are the most computationally intensive? It is worthwhile to do initial performance analysis on typical data sets, to be sure the hot spots in the program are being targeted. When you know which parts of the program can benefit from parallelization, you can consider different patterns for breaking down the problem. Key elements to examine are:

- Function calls

- Loops

- Large data structures that could be operated on in chunks

- Structure the algorithm(s) to exploit concurrency: Ideally, you can identify ways to parallelize the computationally intensive parts:

- Break down the program into tasks that can execute in parallel.

- Identify data that is local to each subtask.

- Group subtasks so that they execute in the correct order.

- Analyze dependencies among tasks.

The major challenges faced during parallelization of the programs are:

- Data dependencies exist.

- Overhead in synchronizing concurrent memory accesses or transferring data between different processor elements and memory might exceed any performance improvement.

- Partitioning work is often not obvious and can result in unequal units of work.

- What works in one parallel environment might not work in another, due to differences in bandwidth, topology, hardware synchronization primitives, and so forth.

All levels of parallelism are already available with the CBE. These features can be used to our advantage to mitigate some challenges posed by software parallelization. The CBE processor provides a foundation for many levels of parallelization. Starting from the lowest, fine-grained parallelization SIMD processing up to the highest, course-grained parallelization networked multiprocessing with the CBE processor provides many opportunities for concurrent computation. The levels of parallelization include:

- Dual-issue superscalar microarchitecture

- Multithreading

- Multiple execution units with heterogeneous architectures and differing capabilities

- Shared-memory multiprocessing

- SIMD processing

#### 3.2.3 Instruction Sets

As mentioned earlier, in CBEA the PPE is focused on control-intensive tasks and the SPEs are focused on computation-intensive tasks. The two types of processors have different instruction sets due to their different functionality.

Based on our previous discussion in Chapter 2 the instruction set for the PPE is an extended version of the PowerPC instruction set. The extensions consist of the Vector/SIMD Multimedia Extension instruction set plus a few additions and changes to PowerPC instructions. The instruction set for the SPEs is a new SIMD instruction set, the Synergistic Processor Unit Instruction Set Architecture, with accompanying C/C++ intrinsics. It also has a unique set of commands for managing DMA transfer (gets and puts - discussed in later sections of this chapter), external events, interprocessor messaging (mailboxes), and other functions.

Although the PPE and the SPEs execute SIMD instructions, their instruction sets are different, and programs for the PPE and SPEs must be compiled using different compilers. These compilers generate code streams for two completely different instruction sets.

To conclude, even though a high-level language such as C or C++ code can be used for the CBE processor, an understanding of the PPE and SPE machine instructions adds considerably to a software developer's ability to produce efficient, optimized code.

#### 3.3 Communication between PPE and SPE

Before understanding how processors communicate with each other, it is important to know about the types of storage domains the processors use to move data. In CBE there are three types of storage domains - one main-storage domain, eight SPE local storage domains, and eight SPE channel domains, as shown in Figure 3.4. The main-storage domain, which is the entire effective-address space, can be configured by the PPE operating system to be shared by all processors and memory-mapped devices in the system (all I/O is memory-mapped). However, the local-storage and channel problem-state (user-state) domains are private to the SPU, LS, and MFC of each SPE.

Figure 3.4: The Cell Storage Domains

Finally, using the defined communication mechanism implemented in hardware between the processors, we move data to enable interaction between them.

The three primary communication mechanisms between the PPE and SPEs are mailboxes, signal notification registers, and DMAs. This thesis focuses on understanding only mailboxes and DMA transfers, because only these two mechanisms

have been used in implementing the framework. They are explained in the next two sub-sections.

#### 3.3.1 Mailboxes

Mailboxes are the best way to send fast dedicated 32-bit messages between processors. Thus, whenever the processors need to communicate some information that is less than or equal to 32-bits, mailboxes are our best bet; for example, in the case of our framework, addresses of certain structures and variables, sending acknowledgements on receiving specific data, etc., are communicated using the mailboxes. Each SPE has three mailboxes, for sending, receiving and buffering 32-bit messages from the SPE to the PPE. Two mailboxes (the SPU Write Outbound Mailbox) are provided for sending messages from the SPE to the PPE. One mailbox (the SPU Read Inbound Mailbox) is provided for sending messages from PPE to the SPE.

PPE is often used as an application controller, managing and distributing work to the SPEs. A large part of this task may involve loading main storage with data to be processed, then notifying an SPE by means of a mailbox. The SPE can also use its outbound mailboxes to inform the PPE that it has finished with a task. An SPE sends a mailbox message by writing the 32-bit message value to either of its two outbound mailbox channels. The PPE can read a message in an outbound mailbox by reading the MMIO register in the SPE's MFC that is associated with the mailbox channel. Likewise, the PPE sends messages to the SPE's inbound mailbox by writing the associated MMIO register.

Following is a detailed explanation of how *SPU* Inbound and Outbound Mailboxes work along with examples of how to use the functions. This is essential because: (1) it enables us to follow the low level code of framework, and (2) knowing the mechanism of how mailboxes work may also help developers to implement their own mailbox messages.

#### 3.3.1.1 *SPU* Outbound Mailboxes

The MFC provides two one-entry mailbox channels - the *SPU* Write Outbound Mailbox and the *SPU* Write Outbound Interrupt Mailbox - for sending messages from the SPE to the PPE. We use the write outbound mailbox channel in our

implementation for communication. Further details about the channel as well as the functions that are used at the PPE and SPE side are described below.

*SPU* Write Outbound Mailbox Channel: SPE software writes to the *SPU* Write Outbound Mailbox channel to put a mailbox message in the *SPU* Write Outbound Mailbox. This write-channel instruction will return immediately if there is sufficient space in the *SPU* Write Outbound Mailbox Queue to hold the message value. If there is insufficient space, the write-channel instruction will stall the SPU until the PPE reads from this mailbox.

SPE Side: On the SPE side the function  $spu\_write\_out\_mbox()$  writes to the SPU Write Outbound Mailbox and stalls until space is available. Once the  $mbox\_data$  is successfully written to the SPU Write Outbound Mailbox on the SPE side, the next step is for PPE to read the value. The function used by SPE to send the data is given below:

```

unsigned int mbox_data;

spu_write_out_mbox(mbox_data);

```

PPE Side: Before PPE software can read data from one of the SPU Write Outbound Mailboxes, it must first read the Mailbox Status Register to determine that unread data is present in the SPU Write Outbound Mailbox; otherwise, stale or undefined data may be returned. To determine that unread data is available in the SPU Write Outbound Mailbox, PPE software reads the Mailbox Status Register and extracts the count value from the SPU Out Mbox Count field. If the count is non-zero, then at least one unread value is present. If the count is '0', PPE software should not read the SPU Write Outbound Mailbox Register because it will get incorrect data and should poll the Mailbox Status Register. The function used to read the Mailbox Status Register is int\_spe\_out\_mbox\_status (spe\_context\_ptr\_t spe) where the parameter spe specifies the SPE context for which the SPU Outbound Mailbox has to be read. PPE polls to read the SPU channel.

The function used by PPE to read SPU Write Outbound Mailbox Channel is:

The description of parameters of the function is as follows:

- spe Specifies the SPE context for which the SPU Outbound Mailbox has to be read.

- mbox\_data A pointer to an array of unsigned integers of size count to receive the 32-bit mailbox messages read by the call.

- count The maximum number of mailbox entries to be read by this call.

This function returns an integer value - 0, >1 or <1.

- >0 the number of 32-bit mailbox messages read

- 0 No data to be read

- -1 error condition and errno is set appropriately

#### 3.3.1.2 SPU Inbound Mailboxes

The MFC provides one mailbox for a PPE to send information to an SPU: the SPU Read Inbound Mailbox. This mailbox has four entries; that is, the PPE can have up to four 32-bit messages pending at a time in the SPU Read Inbound Mailbox. More details about the channel and the functions used at the SPE and PPE side are given in the following subsections.

**SPU Read Inbound Mailbox Channel:** SPU Read Inbound Mailbox Channel: If the SPU Read Inbound Mailbox channel has a message, the value read from the mailbox is the oldest message written to the mailbox. If the inbound mailbox is empty, the SPU Read Inbound Mailbox channel count will read as '0'.

**PPE** Side: This function writes up to count messages to the SPE inbound mailbox for the SPE context *spe*. This call may be blocking or non-blocking, depending on behavior. The blocking version of this call is particularly useful to send a sequence of mailbox messages to an SPE program without further need for synchronization. The non-blocking version may be advantageous when using SPE events for synchronization in a multi-threaded application. *spe\_in\_mbox\_status* can be called to ensure that data can be written prior to writing the *SPU* inbound mailbox. *spe\_in\_mbox\_status*(*spe\_context\_ptr\_t spe*) function fetches the status of

the *SPU* Inbound Mailbox for the SPE context specified by the *spe* parameter. A  $\theta$  value is returned if the mailbox is full. A non-zero value specifies the number of available (32-bit) mailbox entries. The function to write to the *SPU* Read Inbound Mailbox is given below:

```

#include <libspe2.h>

int spe_in_mbox_write (spe_context_ptr_t spe,

unsigned int *mbox_data, int count,

unsigned int behavior)

```

- spe Specifies the SPE context of the SPU Inbound Mailbox to be written.

- mbox\_data A pointer to an array of count unsigned integers containing the 32-bit mailbox messages to be written by the call.

- count The maximum number of mailbox entries to be written by this call.

- behavior Specifies whether the call should block until mailbox messages are written.

There are four possible values for behavior, given in Table 3.3.1.2

Table 3.1: Values of Behavior

After the PPE writes the mbox\_value, the SPE has to read the same from the SPU Read Inbound Mailbox.

*SPE* **Side:** SPE software can use a read-channel funcion on the *SPU* Read Inbound Mailbox channel to read the contents of its *SPU* Read Inbound Mailbox. This channel read will return immediately if any data written by the PPE is waiting in the *SPU* Read Inbound Mailbox. This read-channel function will cause the SPU to stall if the *SPU* Read Inbound Mailbox is empty.

```

unsigned int mbox_data;

mbox_data = spu_read_in_mbox();

```

Although the mailboxes are primarily intended for communication between PPE and SPEs, they can also be used for communication between an SPE and other SPEs, processors, or devices.

## 3.3.2 Direct Memory Access

When the PPEs and SPEs have to transfer larger amounts of data or instructions they use DMAs. Architecturally the DMAs are implemented to support the transfer of large amounts (maximum 16 kB) of data or instructions between the processors at a single instant. As our framework needs to support data transfers of size 10 kB, knowing to how to use and implement DMAs properly is essential.

MFC's DMA Controller (DMAC) implements DMA transfers of instructions and data between the SPUs LS and main storage. Programs running on the associated SPU, or the PPE, can issue the DMA commands. The MFC executes DMA commands autonomously, which allows the SPU to continue execution in parallel with the DMA transfers. Each DMAC can initiate up to 16 independent DMA transfers to or from its LS.

#### 3.3.2.1 DMA Transfers

To initiate a DMA transfer, software on an SPE uses a channel instruction to write the transfer parameters to the MFC command queue channels. An SPE can only fetch instructions from its own LS. An SPE or PPE performs data transfers between the SPE's LS and main storage primarily using DMA transfers controlled by the MFC DMA controller for that SPE. Software on the SPE's SPU interacts with the MFC through channels, which enqueue DMA commands (length of the queue being 16) and provide other facilities, such as mailboxes and signal notification. An SPE program accesses its own LS using a local storage address (LSA). The LS of each SPE is also assigned a real address (RA) range within the systems memory map. This allows privileged software to map LS areas into the effective address (EA) space, where the PPE, SPEs, and other devices that generate EAs can access the LS. Each SPE's MFC serves as a data-transfer engine. DMA trans-

fer requests contain both an LSA and an EA. Thus, they can address both a SPE's LS and main storage and thereby initiate DMA transfers between the domains.

The MFC accomplishes this by maintaining and processing an MFC command queue. The queued requests are converted into DMA transfers. Each MFC can maintain and process multiple in-progress DMA command requests and DMA transfers. The MFC can also autonomously manage a sequence of DMA transfers in response to a DMA-list command from its associated SPU. Each DMA command is tagged with a 5-bit Tag Group ID. Software can use this identifier to check or wait on the completion of all queued commands in one or more tag group.

**DMA commands:** The majority of MFC commands initiate DMA transfers; these are called DMA commands. The basic DMA commands are the *get* and *put*. Since the LSs of the SPEs and the I/O subsystems are typically mapped into the effective address space, DMA commands can transfer data between the LS and these areas as well. Regardless of the initiator (SPU, PPE, or other device), DMA transfers up to 16 kB of data between LSs and main memory or between LSs. An MFC supports naturally aligned DMA transfer sizes of 1, 2, 4, 8, and 16-bytes and multiples of 16-bytes. The performance of a DMA transfer can be improved when the source and destination addresses have the same quadword offsets within a 128-byte cache line.

• *put* (put[s]) command transfers the number of bytes specified by the transfer size parameter from the local storage address of the corresponding SPU to the effective address (EA).

```

(void) mfc_put(volatile void *ls, uint64_t ea,

uint32_t size, uint32_t tag, uint32_t tid,

uint32_t rid)

```

The arguments to this function correspond to the arguments of the spu\_mfcdma64 command: *ls* is the local-storage address, *ea* is the effective address in system memory, *size* is the DMA transfer size (maximum is 16 kB), *tag* is the DMA tag, *tid* is the transfer class identifier, and *rid* is the replacement class identifier.

get command transfers the number of bytes specified by the transfer size parameter from the effective address to the local storage address of the corresponding SPU.

```

(void) mfc_get(volatile void *ls, uint64_t ea,

uint32_t size, uint32_t tag, uint32_t tid,

uint32_t rid)

```

The arguments to this function correspond to the arguments of the spu\_mfcdma64 command: *ls* is the local-storage address, *ea* is the effective address in system memory, *size* is the DMA transfer size (maximum is 16 kB), *tag* is the DMA tag, *tid* is the transfer class identifier, and *rid* is the replacement class identifier, same as above.

When MFC commands are entered into the command queue, each command in the queue is tagged with a 5-bit tag-group identifier, called the *MFC command tag identifier*. The identification tag can be any value between 0 and 31. The same identifier can be used for multiple MFC commands to create a tag group containing all the commands currently in the queue with the same command tag. Software can use the MFC command tag to check the completion of all queued commands in a tag group. In our implementation the transfer class identifier and replacement class identifier are both 0 and more information on them is not required.

After MFC commands are entered into the command queue, we might want to know the status of these MFC commands. There are certain MFC DMA command functions that can be used to check the completion of MFC commands or the status of entries in the MFC DMA queue. The function used to determine the status of the MFC DMA command is *mfc\_read\_tag\_status*. Each bit of a returned value indicates the status of each tag group. If set, the tag group has no outstanding operation (that is, commands completed) and is not masked by the query.

In our implementation, out of the many provided MFC DMA status functions, we use  $mfc\_write\_tag\_mask$  and  $mfc\_read\_tag\_status\_all()$ . We explain these two functions in more detail below.

mfc\_write\_tag\_mask - A tag mask is set to select the MFC tag groups to be included in the query operation, where the parameter mask in the function is the DMA tag group query mask. Each bit of the mask indicates the tag group. Implementation:

```

(void) mfc_write_tag_mask (uint32_t mask)

```

For example in an  $mfc\_get()$  command suppose the tag group identifier is given as 7, then the 7th bit in the tag group identifier is set to 1. Thus, the  $mfc\_write\_tag\_mask$  function is implemented as  $mfc\_write\_tag\_mask$  (1 << 7).

• *mfc\_read\_tag\_status\_all()* - A request is sent to update tag status when all enabled MFC tag groups have a "no operation outstanding" status. The processor waits for the status to be updated. Implementation:

```

(uint32_t) mfc_read_tag_status_all(void)

```

Thus, the MFC waits till all the DMA commands in the tag group (tag mask is already set for all the commands with the same tag group) have completed.

# 3.4 Chapter Conclusion

In this chapter, I explained the various unique software features of CBEA that enhance our control over the interconnection architecture. This helps to understand the complexity involved in abstracting away from the low level bus architectural constraints to successfully implement the scheduling framework.

I also described in detail the different application partitioning models, creation of threads that are used to send processing requests to different processors, the PPE and SPE instruction sets and finally an overview of how PPE and SPEs interact.

# **CHAPTER 4**

# BACKGROUND WORK: BUS SCHEDULING ALGORITHMS

Our research group focused on developing an abstraction of the scheduling problem as well as an effective methodology that predictably schedules the multiprocessor bus. My key contribution to this effort was to build a framework that would allow the team to implement and test the performance of a class of scheduling algorithms for CBEA, while maintaining high throughput. While the focus of this thesis is to understand the framework; it is also important to know the scheduling algorithm, as it is important background material needed to appreciate the overall solution. In this chapter, I briefly describe the real-time algorithm that was designed.

The research team proposed to employ a software-controllable Multi-Domain Ring Bus (MDRB) architecture to increase system predictability and tighten WCET estimation. The problem of scheduling periodic real-time transactions on MDRB is challenging because the bus allows multiple non-overlapping transactions to be executed concurrently, and because the degree of concurrency depends on the topology of the bus and of executed transactions. The team proposed a practical abstraction for the scheduling problem together with novel scheduling algorithms. The first algorithm is optimal for transaction sets under restrictive assumptions while the second induces a competitive sufficient schedulable utilization bound for more general transaction sets.

This chapter is divided into three sections. The first section briefly reviews important terminology that is needed to understand the algorithms and implementation. This will also be helpful in understanding the description of the implementation of the framework (Chapter 5). The second section describes Real-Time Bus Transaction and Scheduling Model. The last section presents the scheduling algorithm for the proposed real-time transaction sets on the ring buses. Also, the relevant proofs that demonstrate the effectiveness of these algorithms have been included.

# 4.1 Terms and Terminology

#### 4.1.1 Transaction

An event in which data is transferred from one processor to another is referred to as a transaction. We model three types of transactions in our implementation, which are described below.

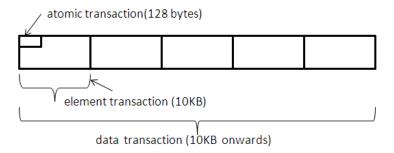

#### 4.1.1.1 Atomic Transaction

An *atomic* transaction (see Figure 4.1) is defined as the smallest non-interruptible transaction on the bus. The size of an *atomic* transaction on the EIB is 128 bytes.

Figure 4.1: Types of Transactions

### 4.1.1.2 Element Transaction

An *element* transaction is defined as a transaction that is started by a transfer command issued by the bus scheduler. In other words, an *element* transaction is a sequence of *atomic* transactions that are scheduled without interrupts from the bus scheduler's standpoint. The size of an *element* transaction is defined in terms of the number of *atomic* transactions it is composed of.

#### 4.1.1.3 Data Transaction

It represents a request made by an application for transferring a certain amount of data between CBEA's components. A *data* transaction comprises one or more *element* transactions. The size of a *data* transaction is defined in terms of the number of *atomic* transactions it is composed of.

The bus scheduler starts a transaction by first putting the data of the transaction into a DMA buffer of the MFC and then issues a *sending command* to the MFC. The transaction is transferred by the MFC in a hop-by-hop manner from the source to the destination through the shortest possible bus segment. For example, in Figure 2.4, the route of a transaction from SPE1 to SPE2 is SPE1-PPEMIC-SPE0-SPE2 on either of the two counterclockwise rings. We define two transactions to be overlapping if they share a segment of their route on the same ring.

Let us call a transaction that is started by a *sending command* an *element* transaction. A 128-byte chunk is an *atomic* transaction which operates in a non-interrupted manner. However, between *atomic* transactions of an *element* transaction, the bus may transfer *atomic* transactions of other *element* transactions on the same bus segment. In other words, an *element* transaction can be interrupted between its *atomic* transactions.

As already mentioned previously in Chapter 2, every *atomic* transaction goes through five phases sequentially, out of which three phases have a higher significance in terms of building the schedules: the *command*, the *arbitration*, and the *data* phase. Consequently, the remaining two phases, the *arbitration* and *data* phases, are called the *post-command* phase. During the *command* phase of an *atomic* transaction, the arbiter sets up a route for the transaction and puts it into a *post-command* phase queue. Let the command phase latency be  $L^c$ . The command phase latency can be hidden by pipelining.

#### 4.1.2 Contention

A bus interface unit (BIU) can issue one command every cycle even while the command phase of its previous atomic transaction has not been completed. The arbitration phase starts at the end of the command phase. Due to some bus constraints, contention between *atomic* transactions may occur in their post-command phases. A low-level round robin scheduler arbitrates bus accesses between contending transactions stored in the post-command phase queue. This phase occurs when the BIU has to wait for bus access due to the contention between atomic transactions on the bus. There are three types of contentions described in the following.

### 4.1.2.1 Overlap Contention

Overlap contention occurs when there is an atomic transaction finishing the command phase while there are other overlapping transactions in their post-command phases. The atomic transaction has to wait at least until the other active overlapping transactions complete. Suppose if on one of the clockwise rings two element transactions, SPE0 to SPE1 and SPE3 to SPE5 (Figure 4.2), are in their postcommand phases. An atomic transaction SPE 1 to SPE 5 on the same ring has to wait for the overlapping transaction SPE3 to SPE5 to finish. Even though there are currently two transactions and according to the bus architecture, there can be three atomic transactions simultaneously on the ring. The atomic transaction from SPE1 to SPE5 has to wait due to overlap on the bus segment.

Figure 4.2: Overlap Contention

## 4.1.2.2 Overload Contention

Overload contention occurs when there is an atomic transaction finishing the command phase while, on the same ring, there are at least three non-overlapping transactions in their post-command phases (see Figure 4.3). Because each bus ring can support at most three atomic transactions at a point of time, the atomic transaction has to wait at least until any one of the previously active atomic transactions completes. For example, suppose there are three transactions SPE0 to SPE1, SPE3 to SPE5 and SPE4 to SPE2; if you want to start another transaction SPE2 to SPE0, you need to wait for any one of the above transactions to complete because at any given time there can be only three non-overlapping simultaneous transactions on the bus ring.

Figure 4.3: Overload Contention

#### 4.1.2.3 Start-Time Contention

Start-time contention occurs when there is an atomic transaction finishing the command phase while on the same ring there are k < 3 other non-overlapping transactions which have been in their post-command phases for less than three cycles. Since a bus ring can only start the data phase of one atomic transaction every  $L^o = 3$  cycles, the atomic transaction has to wait for at most  $k * L^o$  cycles. Let us define the delay due to the start-time contention to be the start-time latency.

# 4.2 Real-Time Bus Transaction and Scheduling Model

We consider a scheduling problem where applications request periodic data transfers (data transactions) on the bus. A data transaction comprises of an infinite number of periodic jobs.

Without loss of generality, let the bus elements be indexed clock-wise. We define  $\mathcal{T}$  as the set of data transactions  $\mathcal{T} = \{\tau_i : i = [1, N]\}$ . A data transaction  $\tau_i$  is characterized by a tuple  $\tau_i = (e_i, p_i, \epsilon_i^1, \epsilon_i^2)$  where  $e_i$  is the time that the bus spends to transmit a job of  $\tau_i$ ,  $p_i$  is the period of  $\tau_i$ , and  $\epsilon_i^1, \epsilon_i^2$  are the two indexes of the two endpoints which are called the first and the second index of  $\tau_i$ , respectively. Each job must complete within its period, i.e. relative deadlines are equal to periods. A transaction has two endpoints  $\epsilon_i^1$  and  $\epsilon_i^2$  if it uses all bus elements in  $[\epsilon_i^1, \epsilon_i^2]$  in the clockwise direction. Transaction  $\tau_i$  is said to go through element  $\epsilon$  if  $\epsilon \in [\epsilon_i^1, \epsilon_i^2]$  (excluding the second endpoint of  $\tau_i$ ). The bus utilization

$u_i$  of  $\tau_i$  is calculated as  $u_i = e_i/p_i$ . We assume that all data transactions arrive at time 0. Let hyper-period h of  $\mathcal{T}$  be the least common multiple of the periods of all transactions in  $\mathcal{T}$ .

Two transactions are said to *overlap* and cannot be transferred concurrently on the bus if they use the same bus segment between any two elements. Based on the endpoint definition, it is obvious that two transactions overlap if and only if they go through the same element. Given a data transaction set  $\mathcal{T}$ , we define an overlap indicating function  $OV: \mathcal{T} \times \mathcal{T} \mapsto \{0,1\}$  where  $OV(\tau_i, \tau_j) = 1$  if  $\tau_i$  and  $\tau_j$  overlap, and 0 otherwise.

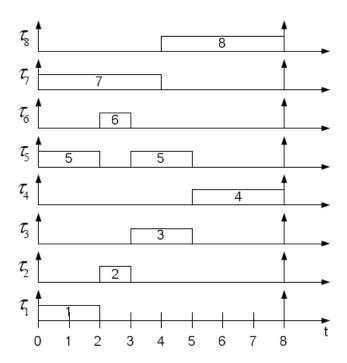

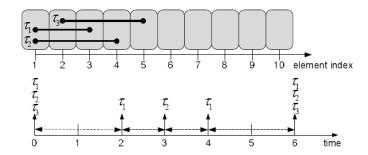

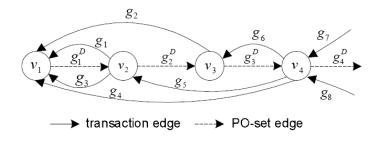

A pairwise overlap set (PO-set)  $\mathcal{D}$  is defined as a maximal subset of  $\mathcal{T}$  such that  $\forall \tau_i, \tau_j \in \mathcal{D}: OV(\tau_i, \tau_j) = 1$ . For convenience, we consider that a non-overlapping transaction belongs to a PO-set that contains only that transaction. In general a transaction may belong to more than one PO-set. Figure 4.4 shows an example of a transaction set with four PO-sets:  $\mathcal{D}_1 = \{\tau_1, \tau_2, \tau_3, \tau_4\}, \mathcal{D}_2 = \{\tau_2, \tau_4, \tau_5\}, \mathcal{D}_3 = \{\tau_4, \tau_5, \tau_6\}, \mathcal{D}_4 = \{\tau_7, \tau_8\}$ . Let the total number of PO-sets in a transaction set be  $N^{\mathcal{D}}$ . Notice that although  $\tau_2$  and  $\tau_6$  have one common endpoint (element 5), they do not overlap because they do not share any bus segment. Since each PO-set contains at least one element different from each other PO-set and transactions are arranged in an one dimension space,  $N^{\mathcal{D}} \leq N$ .

Figure 4.4: Non-circular Transaction Set

A transaction set is said to be *circular* if its overlapping transactions create a cycle on the bus and to be *non-circular* otherwise. Figures 4.4 and 4.5 show an example of a non-circular and a circular transaction set, respectively. A non-circular transaction set can be represented as a set of overlapping intervals on an indexed straight line where each interval corresponds to a transaction and the straight line is indexed by the indexes of the bus elements. Figure 4.6 shows the indexed straight line representation of the non-circular transaction set shown in

Figure 4.5: Circular Transaction Set

Figure 4.6: Indexed Straight Line Representation

Figure 4.4. Let the left-most transaction on the straight line be the *first* transaction. If there are more than one left-most transactions, any one of them can be the first transaction. For simplicity, we index the bus elements such that the first transaction has the first index to be the smallest index.

Due to the discrete nature of transactions' execution times and periods, we adopt the discrete scheduling model used in [7]. More specifically, we assume that every transaction's execution time and period are integral values. Scheduling decisions are also made at integral values of time, starting from 0. The real interval between time  $t \in \mathbb{N}$  and time t+1, i.e. [t,t+1), is called *slot* t. A schedule S is defined as a function  $S: \Gamma \times \mathbb{N} \mapsto \{0,1\}$  where  $S(\tau_i,t)=1$  if and only if  $\tau_i$  is scheduled at slot t. A schedule S is *valid* if and only if according to S, it *never* happens that a transaction is scheduled in the same slot together with one or more other transactions that overlap with it.

Given the constraint on overlapping transactions, a necessary condition on the schedulability of a transaction set can be easily derived as in Theorem 4.2.1.

**Theorem 4.2.1.** A transaction set T is schedulable only if:

$$\forall \mathcal{D} \subset \mathcal{T} : u^{\mathcal{D}} = \sum_{\forall \tau_i \in \mathcal{D}} u_i \le 1.$$

(4.2.1)

*Proof.* Since, by definition, no two transactions of a PO-set  $\mathcal{D}$  can be scheduled

concurrently, all transactions of  $\mathcal{D}$  must be scheduled in sequence. In other words, the transactions of  $\mathcal{D}$  can be considered to be sharing one resource. Therefore, Inequality 4.2.1 must be satisfied.

Let  $\mathcal{E}(k)$  be a set of all transactions in  $\mathcal{T}$  that go through same bus element indexed k. The following lemma is necessary for later discussion.

**Lemma 4.2.1.** Given a transaction set T that satisfies the necessary condition, the following inequality holds:

$$\sum_{\forall \tau_i \in \mathcal{E}(k)} u_i \le 1.$$

*Proof.* Since transactions in  $\mathcal{E}(k)$  pairwise overlap, there exists  $\mathcal{D}$  such that  $\mathcal{E}(k) \subseteq \mathcal{D}$ . Therefore the lemma is implied by Theorem 4.2.1.

# 4.3 Scheduling Algorithms for Ring Buses

In this section we present our scheduling algorithms for the proposed real-time transaction sets on the ring buses. The discussion is divided into three parts.

First, we propose an algorithm, namely POBase, which schedules every non-circular transaction set whose transactions have the *same* period. We will prove that the necessary condition (Theorem 4.2.1) is also the sufficient condition for same-period non-circular transaction set to be schedulable by POBase. Therefore, POBase is optimal for these transaction sets.

Second, a scheduling algorithm, namely POGen, is proposed to schedule non-circular transaction sets whose transactions do not have the same period. POGen, which is built based on POBase, can schedule all transaction sets for whose PO-set utilizations satisfy the following utilization bound:

$$\forall \mathcal{D} \subset \mathcal{T} : u^{\mathcal{D}} \le \frac{\mathsf{L} - 1}{\mathsf{L}},$$

(4.3.1)

where L is defined as the greatest common divisor of all transaction periods. Although the utilization bound is sufficient, it approximates 1 when L is large. We believe that this assumption holds in most practical real-time applications [8]. As we will show in the implementation section, with the speed of the state of the art

multicore chip buses [4], the practical time slot size is about 1  $\mu$ s to 1  $\mu$ s. Meanwhile, the period granularity in practical real-time applications [8] is at the level of milliseconds. That means L has practical values ranging from 10 to 100 time units.

Finally, we will discuss the issue of scheduling circular transaction sets and our proposed initial solution.

## 4.3.1 The POBase Algorithm