Center for Reliable and High-Performance Computing

DO NOT Remove

ProperCAD:

A PORTABLE

OBJECT-ORIENTED

PARALLEL ENVIRONMENT

FOR VLSI CAD

Balkrishna Ramkumar and Prithviraj Banerjee

Coordinated Science Laboratory

College of Engineering

UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN

| SECURITY C                  | ASSIFIED LASSIFICATION                                                                                                           | OF THIS PAGE                                                                                                                                                                          |                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                                                                      |                                                                                                        |                                                            |                                           |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------|

|                             |                                                                                                                                  |                                                                                                                                                                                       | REPORT DOCU                                                                                                                                                                                                                    | MENTATION                                                                                                                                             | PAGE                                                                                                                 |                                                                                                        |                                                            |                                           |

|                             | SECURITY CLAS                                                                                                                    | SIFICATION                                                                                                                                                                            |                                                                                                                                                                                                                                | 1b. RESTRICTIV                                                                                                                                        |                                                                                                                      |                                                                                                        |                                                            | Table 84                                  |

|                             | assified                                                                                                                         | ON AUTHORITY                                                                                                                                                                          |                                                                                                                                                                                                                                | None                                                                                                                                                  |                                                                                                                      |                                                                                                        |                                                            |                                           |

| Za. SECURI                  | Y CLASSIFICATIO                                                                                                                  | ON AUTHORITY                                                                                                                                                                          |                                                                                                                                                                                                                                |                                                                                                                                                       | N/AVAILABILIT                                                                                                        |                                                                                                        |                                                            |                                           |

|                             |                                                                                                                                  | WNGRADING SCHE                                                                                                                                                                        |                                                                                                                                                                                                                                | Approve                                                                                                                                               | d for publi                                                                                                          | ic rel                                                                                                 | ease;                                                      |                                           |

| 4. PERFORM                  | ING ORGANIZA                                                                                                                     | TION REPORT NUM                                                                                                                                                                       | BER(S)                                                                                                                                                                                                                         | 5. MONITORING                                                                                                                                         | G ORGANIZATIO                                                                                                        | N REPOR                                                                                                | T NUMBE                                                    | R(S)                                      |

| UILU-E                      | NG-93-2205                                                                                                                       | CRH                                                                                                                                                                                   | C-93-04                                                                                                                                                                                                                        |                                                                                                                                                       |                                                                                                                      |                                                                                                        |                                                            |                                           |

| Coord                       | of PERFORMING<br>inated Sci<br>rsity of I                                                                                        |                                                                                                                                                                                       | 6b. OFFICE SYMBOL<br>(If applicable)<br>N/A                                                                                                                                                                                    | 7a. NAME OF I                                                                                                                                         | MONITORING OF Semic                                                                                                  | RGANIZAT                                                                                               | or Res                                                     | search Corp                               |

| 6c. ADDRES                  | S (City, State, ar                                                                                                               | nd ZIP Code)                                                                                                                                                                          |                                                                                                                                                                                                                                | 7b. ADDRESS (C                                                                                                                                        | City, State, and                                                                                                     | ZIP Code)                                                                                              |                                                            |                                           |

|                             | W. Springf<br>a, IL 618                                                                                                          | ield Avenue<br>01                                                                                                                                                                     |                                                                                                                                                                                                                                |                                                                                                                                                       | ield, CA                                                                                                             |                                                                                                        | Resea                                                      | arch Triangle                             |

| 8a. NAME O                  | F FUNDING/SPO<br>ZATION                                                                                                          | ONSORING<br>7a                                                                                                                                                                        | 8b. OFFICE SYMBOL (If applicable)                                                                                                                                                                                              | 9. PROCUREME                                                                                                                                          | NT INSTRUMENT                                                                                                        | IDENTIF                                                                                                |                                                            |                                           |

| 8c. ADDRESS                 | (City, State, and                                                                                                                | d ZIP Code)                                                                                                                                                                           |                                                                                                                                                                                                                                | 10. SOURCE OF                                                                                                                                         | ELINDING NUM                                                                                                         | 2525                                                                                                   |                                                            |                                           |

|                             |                                                                                                                                  |                                                                                                                                                                                       |                                                                                                                                                                                                                                | PROGRAM                                                                                                                                               | PROJECT                                                                                                              | TASK                                                                                                   |                                                            | WORK UNIT                                 |

|                             |                                                                                                                                  | 7b                                                                                                                                                                                    |                                                                                                                                                                                                                                | ELEMENT NO.                                                                                                                                           | NO.                                                                                                                  | NO.                                                                                                    |                                                            | ACCESSION NO                              |

| 11. TITLE (In               | clude Security C                                                                                                                 |                                                                                                                                                                                       |                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                                                                      |                                                                                                        |                                                            |                                           |

| Prop                        | per CAD: A                                                                                                                       | Portable Obj                                                                                                                                                                          | ject-oriented Par                                                                                                                                                                                                              | allel Enviro                                                                                                                                          | onment for                                                                                                           | VLSI C                                                                                                 | AD                                                         |                                           |

| 12. PERSONA                 | AL AUTHOR(S)                                                                                                                     | Balkrishna Ra                                                                                                                                                                         | amkumar and Prith                                                                                                                                                                                                              | viraj Banerj                                                                                                                                          | jee                                                                                                                  |                                                                                                        |                                                            |                                           |

| 13a. TYPE O                 |                                                                                                                                  | 13b. TIME (                                                                                                                                                                           |                                                                                                                                                                                                                                | 14. DATE OF REPO                                                                                                                                      | ORT (Year, Mont                                                                                                      | th, Day)                                                                                               | 15. PAGI                                                   | E COUNT                                   |

| Techni<br>16. SUPPLEM       | ENTARY NOTAT                                                                                                                     | FROM                                                                                                                                                                                  | то                                                                                                                                                                                                                             | 93- 01-                                                                                                                                               | -29                                                                                                                  |                                                                                                        | 41                                                         |                                           |

|                             |                                                                                                                                  |                                                                                                                                                                                       |                                                                                                                                                                                                                                |                                                                                                                                                       |                                                                                                                      |                                                                                                        |                                                            |                                           |

| 17.                         | COSATI                                                                                                                           | CODES                                                                                                                                                                                 | 18. SUBJECT TERMS (C                                                                                                                                                                                                           | Ontinue on sever                                                                                                                                      | - id                                                                                                                 |                                                                                                        |                                                            |                                           |

| FIELD                       | GROUP                                                                                                                            | SUB-GROUP                                                                                                                                                                             | 18. SUBJECT TERMS (Coparalle                                                                                                                                                                                                   | 1 algorithms                                                                                                                                          | parallel                                                                                                             | envir                                                                                                  | nment                                                      | circuit                                   |

|                             |                                                                                                                                  |                                                                                                                                                                                       | extraction, V                                                                                                                                                                                                                  | LSI, and por                                                                                                                                          | table                                                                                                                |                                                                                                        | Jimeire.                                                   | , circuit                                 |

| 19. ABSTRAC                 | T (Continue on                                                                                                                   | reverse if necessary                                                                                                                                                                  | and identify by block n                                                                                                                                                                                                        | umber)                                                                                                                                                |                                                                                                                      | •                                                                                                      |                                                            | B. Carlotter                              |

| o<br>o<br>a<br>a<br>fo<br>w | Most parallemently only on the architect This paper bject-oriented re two-fold. (1 ccomplish this or portable pare are concurred | el algorithms for<br>machines that the<br>ture for which the<br>describes a new p<br>parallel environs<br>) To develop new<br>in two stages. F<br>rallel programminately developing a | VLSI CAD proposed to<br>ey were designed for. A<br>ey are developed and do<br>project under way to a<br>ment for CAD algorith<br>parallel algorithms that<br>irst, we are developing<br>ag called CHARM<br>C++ environment the | o date have one is a result, algori o not port easily ddress this prob hms (ProperCa t run in a portal g CAD algorithm developed at hat is truly obje | thms designed to other para elem. We are of AD). The object-orier as using a generate the University ct-oriented and | to date a<br>llel archi<br>levelopin<br>ctives of<br>nted envi<br>eral purp<br>y of Illin<br>d special | tectures ag a Por this respondence planting. See tized for | ndent  rtable earch t. We tform cond, CAD |

| pa                          |                                                                                                                                  | ial interface. This                                                                                                                                                                   | s will permit the paral                                                                                                                                                                                                        | lel algorithm to                                                                                                                                      | benefit from fu                                                                                                      | iture dev                                                                                              | relopmer<br>back)                                          | nts in                                    |

DTIC USERS

Unclassified

22b. TELEPHONE (Include Area Code) 22c. OFFICE SYMBOL

INICI ACCIDION

☑UNCLASSIFIED/UNLIMITED ☐ SAME AS RPT.

22a NAME OF RESPONSIBLE INDIVIDUAL

DD FORM 1473, 84 MAR

#### 19. continued

We describe one CAD application that has been implemented as part of the ProperCAD project: flat VLSI circuit extraction. The algorithm, its implementation, and its performance on a range of parallel machines are discussed in detail. It currently runs on an Encore Multimax, a Sequent Symmetry, Intel iPSC/2 and i860 hypercubes, a NCUBE 2 hypercube, and a network of Sun Sparc workstations. We also provide performance data for other applications that have been developed: namely test pattern generation for sequential circuits, parallel logic synthesis and standard cell placement.

# ProperCAD: A Portable Object-oriented Parallel Environment for VLSI CAD\*

Balkrishna Ramkumar

Dept. of Electrical & Computer Engineering

University of Iowa

Iowa City, Iowa 52242

Prithviraj Banerjee Center for Reliable & High-Perf. Computing University of Illinois Urbana, Illinois 61801

#### Abstract

Most parallel algorithms for VLSI CAD proposed to date have one important drawback: they work efficiently only on machines that they were designed for. As a result, algorithms designed to date are dependent on the architecture for which they are developed and do not port easily to other parallel architectures.

This paper describes a new project under way to address this problem. We are developing a Portable object-oriented parallel environment for CAD algorithms (ProperCAD). The objectives of this research are two-fold. (1) To develop new parallel algorithms that run in a portable object-oriented environment. We accomplish this in two stages. First, we are developing CAD algorithms using a general purpose platform for portable parallel programming called CHARM [6, 12] developed at the University of Illinois. Second, we are concurrently developing a C++ environment that is truly object-oriented and specialized for CAD applications. (2) To design the parallel algorithms around a good sequential algorithm with a well-defined parallel-sequential interface. This will permit the parallel algorithm to benefit from future developments in sequential algorithms.

We describe one CAD application that has been implemented as part of the ProperCAD project: flat VLSI circuit extraction. The algorithm, its implementation, and its performance on a range of parallel machines are discussed in detail. It currently runs on an Encore Multimax, a Sequent Symmetry, Intel iPSC/2 and i860 hypercubes, a NCUBE 2 hypercube, and a network of Sun Sparc workstations. We also provide performance data for other applications that have been developed: namely test pattern generation for sequential circuits, parallel logic synthesis and standard cell placement.

### 1 Introduction

In view of the increasing complexity of VLSI circuits of the future, the requirements on VLSI CAD tools will continuously increase. Parallel processing for CAD applications is becoming gradually recognized as a popular vehicle to support the increasing computing requirements of future CAD tools. Recent research on parallel CAD applications have been reported for a wide variety of

<sup>\*</sup>This research was supported in part by the National Aeronautics and Space Administration under grant NAG 1-613, and in part by the Semiconductor Research Corporation under grant SRC 91-DP-109.

applications such as placement [2, 13, 19, 20], floor planning [11], circuit extraction [3, 4, 14, 25], test generation and fault simulation [17], etc. Parallel processing for VLSI CAD has become a reality in industry as well. Hardware vendors such as Solbourne have already announced products with multiple CPUs in a single workstation. Software CAD vendors such as Mentor have announced products such as CHECKMATE, a parallel design rule checker using multiprocessing, to accelerate a single job. A major limitation with almost all such previous work is that the parallel algorithms have been targeted to run on specific machines like an Intel iPSC/2 hypercube or an Encore shared memory multiprocessor. Such work, although interesting, is not usable by the rest of the VLSI CAD community since the algorithms are not portable to other machines.

A second serious problem also presents itself in the design of parallel algorithms. The software development cycle for parallel algorithms is considerably longer than for sequential algorithms. This has two important implications. The first is that they are considerably more costly to develop than sequential algorithms. This is only exacerbated by the lack of portability across parallel machines. The second implication is a more pragmatic one. Given the fast pace of progress in the development and improvement of sequential algorithms for CAD applications, for a given application, sequential algorithms frequently outperform parallel algorithms due to the longer development time of the latter. For example, this is evident in parallel test pattern generation. The latest version of HITEC [16], a uniprocessor test pattern generation program for sequential circuits is already comparable in performance and is slightly better in quality of results than a recent parallel algorithm for test pattern generation [17].

A related issue in the development of parallel algorithms is that certain approaches are inherently parallelizable and others are extremely hard to parallelize. More often than not, the tradeoff between these two approaches is in the quality of results. Cell placement is a good example. The quadrisection algorithm [24] is easily parallelizable and is significantly faster than algorithms based on simulated annealing. However, it cannot produce results comparable to TimberWolf [22], a sequential program that uses simulated annealing (and a host of related tricks) to do cell placement. An interesting possibility would be to use a hybrid of these two (and possibly other) techniques, where, for example, quadrisection could be used for decomposition of the layout area into regions, and TimberWolf would be used for placement in a given region. However, to experiment with such

techniques, it should not be necessary to rewrite the software entirely. Any attempt to rewrite TimberWolf [22] will not only be extremely time consuming, it is also unlikely to be comparable in performance. However, if it is possible to decouple the parallel and sequential algorithms and provide a well defined interface between the two, it may be practical to experiment with hybrid schemes such as these.

It would be presumptuous to assume that it will be trivial to interface the parallel algorithm with the sequential algorithm as described above. For this to be practical, it is imperative that sequential algorithms be written in a modular fashion. Fortunately, object-oriented programming in C++ (or even disciplined C programming) goes a long way in realizing this requirement. Many CAD vendors are already rewriting many of their well-established CAD applications using such disciplined, modular programming methods due to the benefits offered in program design and maintenance.

The most important questions that need to be addressed in the development of parallel algorithms are therefore: "How can we design parallel algorithms that are truly portable across parallel machines?", "How can we exploit good sequential algorithms in the design of parallel algorithms", and "How can parallel algorithms keep pace with future developments in sequential algorithms?" These are the main objectives of a new project to be discussed in this paper.

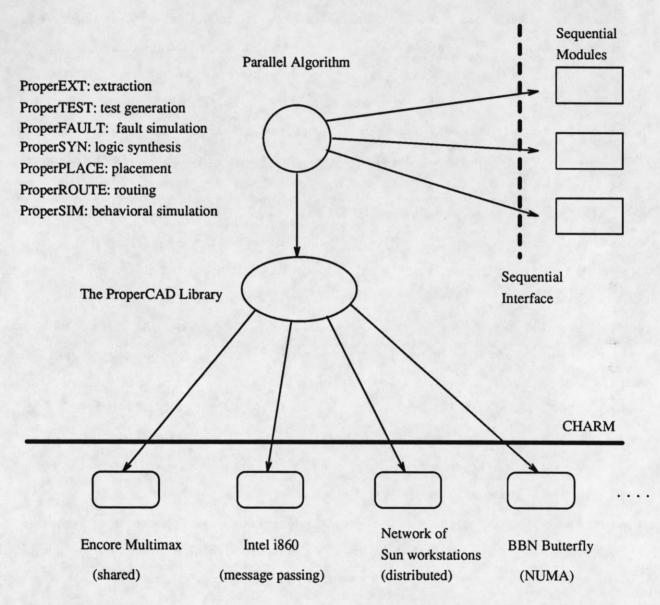

CHARM [6, 12] is a run-time support system for portable parallel programming developed at the University of Illinois. It currently runs on a wide range of parallel machines including shared memory machines, message passing multiprocessors and a network of workstations. We are using CHARM to build a prototype of a Portable object-oriented parallel environment for CAD applications (ProperCAD). Since inception, the ProperCAD project (see Figure 1) is designed to be completed in two phases. In the first phase, we are designing portable parallel algorithms for a large set of CAD applications using CHARM. To date, algorithms for flat extraction, test generation for sequential circuits [18] and combinational logic synthesis [5] and standard cell placement have been designed and implemented. New algorithms for global routing, fault simulation and behavioral simulation are currently under development.

The second phase of the project is expected to take a couple of years. It will involve the design and implementation of a run-time support system for portable parallel programming in C++. This

system, although inspired by CHARM, will be tailored specifically for CAD applications. This will make the programming environment truly object-oriented and will support features like *inheritance* and *classes*. The ProperCAD applications will then be rewritten and ported onto the new C++ platform. The new platform will make it possible to adapt and integrate the parallel applications with software developed by companies like Cadence and Mentor, which are increasingly using C++ as a standard for their software development. Recall that reuse of sequential code is one of the primary objectives of the ProperCAD project. In the second phase of this project, we will also develop a library for the rapid prototyping and development of additional parallel CAD applications. The library will essentially be a parallel data manager that supports data distribution abstractions and primitives designed for an integrated parallel CAD environment. The library can be viewed as as being analagous to the Oct tools [9] distributed by the University of California at Berkeley for uniprocessor CAD applications.

The CHARM system was chosen as the platform for two significant reasons. The first is that it is a working prototype of a run time support system that offers true portability of parallel applications across MIMD machines. Second, although not truly object-oriented, it supports an object-oriented style of programming. This will make porting of the CAD applications to C++ much easier. We discribe the CHARM system briefly in Section 2.

In Section 3, we discuss how flat circuit extraction is expressed as an example of the use of the programming paradigm supported by the ProperCAD environment. The algorithm for circuit extraction presented in this paper has three significant contributions: (1) It is portable across MIMD architectures. (2) It is built around an existing sequential circuit extractor using a well-defined interface. This enables it to benefit from future improvements in the sequential algorithms for circuit extraction. (3) Unlike previous approaches to parallel circuit extraction, it uses an asynchronous coarse-grained data-flow model of execution. This is instrumental in rendering the parallel algorithm scalable on all the target machines. Contributions (2) and (3) together also permit good load balancing and high processor utilization.

Figure 1: A high-level view of the ProperCAD project currently under development using the CHARM parallel programming environment. We list the CAD applications under development above.

# 2 The Parallel Programming Model

CHARM is a run time support system for *portable* parallel programming [6]. It abstracts away all machine dependent features away from an application program and provides a uniform set of primitives that can be used by the application to render their program machine independent. Features like dynamic process creation, mapping of processes to processors, dynamic load distribution and load balancing, scheduling, interprocess communication, are provided by the kernel. These are implemented in the most efficient manner possible on each of the machines that the kernel runs on. These features often complicate the user application considerably. CHARM helps the programmer separate these concerns.

The CHARM kernel supports a message-driven style of execution. Conceptually, it maintains a pool of messages that represent work. The application program can create processes dynamically by creating a message that represents a seed for a new dynamically created object. Information can be exchanged between these objects also via messages. When a message is created it is put in the work pool. The messages in the work pool are distributed (and periodically balanced) across the available processors by the kernel. The kernel services messages in the pool until no more are available. Quiescence is detected; the programmer may take necessary action at this point (for example, printing results).

A CHARM program comprises a set of object definitions. Each object definition has a set of entry points which have C-code associated with them (see Figure 6 for an outline of the object for circuit extraction). Instances of these object definitions may be created dynamically at run time.<sup>2</sup>. Messages may be sent to these objects at one of its entry points, and the servicing of a message entails executing the code associated with the entry point sequentially. No interrupts or blocking (e.g. for synchronous receives) are possible within a code block associated with an entry point. Only one instance of a special object called the *main* object is created. It has special entry points for initialization and detection of quiescence. These do not have messages sent to them unlike normal entry points. The initialization entry point performs data and object initialization during

<sup>&</sup>lt;sup>1</sup>An object is created when this message is serviced.

<sup>&</sup>lt;sup>2</sup>These objects are similar to actors [1], a type of concurrent object. Wegner [26] categorizes actors to be active imperative objects. Note, however, that features like inheritance are not supported by CHARM.

startup. The quiescence entry point is optional; it permits the user to provide the action to be taken upon detection of quiescence. If it is absent, the program terminates.

CHARM also provides a special type of object called a branch office. One instance of the branch office object is created per processor. As with the main object, branches are initialized automatically on the local processors by executing code associated with an Init entry point. Both types of objects permit the declaration of persistent data that is visible only when executing any code associated with the object (or branch). Both types of objects also permit the declaration of procedures or functions as part of its definition. The functions in an object are private to the object, whereas the functions in a branch office may be invoked by other objects. Branch office objects are useful in providing data and program abstraction and have a concurrent object-like behavior. For example, the access to distributed data can be managed by branch office objects. A program may comprise several branch offices, each of which manages a different complex data structure (like a circuit, BDDs, etc.). An example of a branch office object definition is provided in Figure 2.

Another interesting feature of the CHARM kernel is conditional packing. The program definition also includes routines for packing messages into contiguous buffers and unpacking them into a representation used by the program. A pair of such routines are provided for each message type in the program for which packing/unpacking is necessary. These are used by the CHARM kernel on nonshared memory machines when it is necessary for a message to cross process boundaries. Note that for shared memory machines packing is not necessary. Hence, the algorithm runs efficiently on shard memory machines as well.

Other features provided by CHARM are beyond the scope of this paper. Only features that are important to the ensuing sections are discussed above. Further details may be found in [6].

The primary objective of a CHARM program is to create a large number of messages representing parallel work. Typically, this is done by decomposing the problem hierarchically into smaller and smaller subproblems which can be evaluated in parallel, until a threshold is reached. This threshold is user defined, and is used to indicate that subproblems smaller than the threshold are to be evaluated sequentially. Ideally, the threshold determines the point at which it is cheaper to solve a subproblem sequentially in preference to decomposing it further into parallel subcompo-

nents. Determining this threshold accurately is not necessary as long as sufficiently large number of messages are created each of which represents a reasonable amount of work (e.g. > 50 ms). The more the messages available to the kernel, the better its capability to perform dynamic load balancing. The problem decomposition is thus independent of the number of processors available.

CHARM has been ported to a variety of shared memory and nonshared memory machines including the Encore Multimax, the Sequent Symmetry, the Alliant FX/8, the Intel iPSC/2 and i860 hypercubes, the NCUBE 2 hypercube, and a network of Sun workstations. It is currently being ported to the BBN TC2000 Butterfly multiprocessor. Four portable implementations of the CHARM kernel have been developed so far, one for shared memory machines, one for nonshared memory machines, one for NUMA type machines, and one for a network of workstations. Every time a new parallel machine is announced, the kernel can be ported to the new machine with relatively little effort.<sup>3</sup>

### 3 VLSI Circuit Extraction

VLSI circuit layouts are typically described as a collection of rectangles in different mask levels. The problem of circuit extraction is to take such a layout and determine the circuit connectivity, and obtain estimates for various electrical parameters such as resistance of lines, capacitances of nodes and dimensions of devices. The circuit extraction problem has two components: netlist extraction and parameter extraction. The first component involves determination of the electrically connected regions (called nets). To do this, boolean task manipulations are performed on different layers to derive new layers, as specified in a technology file. For example, in CMOS technology, N-type transistors are obtained by intersecting poly, diffusion and pwell layers, whereas P-type transistors are obtained by intersecting poly, diffusion and complement of pwell layers. A new diffusion layer is obtained by intersecting the old layer with the complement of poly.

The rectangles in the device layers are grouped into maximally connected groups, which form the devices. The rectangles in the other layers are grouped into maximally electrically connected sets, which form the nets. The electrical connectivity information is also provided in a technology

<sup>&</sup>lt;sup>3</sup>This is true unless the architecture of the new machine is radically different to existing architectures. In this case, a new implementation of the kernel best suited to the architecture will be developed.

file as mentioned earlier. This gives the layers that electrically connect on overlap. For example, in CMOS technology, the metal and contact layers electrically connect on overlap, so do the diffusion and contact layers.

The parameter extraction component involves device size extraction, parasitic capacitance extraction and resistance extraction of nets. Different models for parameter extraction with varying accuracy and computational requirements have been proposed. The more accurate the model, the more computation intensive it becomes. The HPEX model [23] is used for the circuit extraction algorithm in this paper. For reasons of brevity, we do not discuss it further here.

Sequential circuit extraction is a well studied problem. Several sequential circuit extractors of varying speed and accuracy already exist [7, 8, 10, 15, 21, 23]. Parallel algorithms for circuit extraction have also been recently proposed [3, 4, 14, 25]. These algorithms perform parallel circuit extraction in several phases, including a data distribution phase, a geometric extraction phase, a merge phase, a device extraction phase and a parameter extraction phase. Such approaches involve synchronization at the start of each phase of the execution. For example, it is necessary to uniquely determine the nets and transistors before proceeding to the parameter extraction phase. This reduces the processor utilization, especially on nonshared memory machines.

To improve the load balancing, two schemes were proposed for data distribution: area-based partitioning [3] and point-based partitioning [4]. The former partitions the circuit into different areas each of which was assigned to a processor which performed local netlist and transistor extraction for its region. This can result in load imbalance if certain areas of the circuit are denser than others. This drawback is addressed by a point-based partitioning scheme which which partitions the circuit so as to approximately assign an equal number of rectangles to each processor. This is costlier and more complicated than the area-based scheme, but yields better results for circuits that do not have its rectangles evenly distributed. In the final phase, the complete nets are also distributed across the available processors for load balancing reasons. These load balancing schemes adopted were different for shared memory [4] and message passing machines [3].

The ProperCAD approach requires us to design programs that are not tailored to a particular type of architecture. It also encourages the use of a coarse-grained data-flow style of execution where a operation can be executed as soon as the data necessary to execute it is available. In parallel

circuit extraction, we adopt a hierarchical approach to decomposition. The circuit is partitioned into several regions and each region is assigned to a processor. (The details of the data distribution are provided in Section 3.1.) A sequential algorithm for local geometric extraction is then run on each the regions to determine the nets and transistors in that region. The nets and the transistors touching a border of the region they belong to are deemed to be incomplete. Incomplete nets and transistors are subject to a merge algorithm, whereas local nets and transistors are available for processing using a sequential algorithm for parameter extraction.

The merge algorithm proceeds in a hierarchical manner where at each stage two adjacent regions are merged. Following every stage of the merge algorithm, nets and transistors that become complete are available for parameter extraction. Nets that are available for parameter extraction are load balanced as and when they become complete, to ensure maximum utilization of processors.

As can be seen in the above brief description of parallel circuit extraction, the geometric extraction on each region as well as the parameter extraction are performed using a sequential algorithm. It is easy to see that the best sequential algorithm can be used for this purpose. The focus of the parallel algorithm is now simply that of (1) decomposing of the problem into subproblems, and (2) merging these subproblems together.

However, how can the overhead of parallelization be kept in check? To see this, consider this simple argument. Based on a property of trees, for a branching factor  $\geq 2$ , the number of leaves in a tree is always greater than the number of internal nodes. If it is possible to ensure that the work done at a leaf node in a problem decomposition tree is at least 10 times the work done at an internal node, the work done at the leaf nodes of the decomposition will dominate the execution time (>90%). Thus, for circuit extraction, if we can conform to this rough criterion for decomposition, by calling the best available sequential algorithm for geometric extraction and parameter extraction, the total overhead of the parallel algorithm can be bounded to within 10% of the best sequential algorithm.

The above argument has been simplified somewhat for ease of explanation. However, the conclusion is still valid. We demonstrate this in Section 3.6 where we discuss the performance of the parallel circuit extraction algorithm. In the following discussion, we describe the different phases of circuit extraction in more detail and how our algorithm avoids synchronization between

```

readonly int grainsize;

branch office Rectangle Manager {

HashTableEntry data-distribution[MaxHashSize];

int initmsgcount;

LocalPartitionTree mypartition;

entry Init:

Compute the circuit partitioning to determine which

processor gets which region. The grainsize

determines the depth of the recursive partitioning

entry Receive Partition: (message InitRectangles *msg)

Receive and insert received rectangles into local partition tree

entry ReceiveRectLoad: (message LoadMsg *msg)

Receive the current rectangle load on other processors

entry SendRectangles: (message SendRequest *msg)

Send some of local rectangles to processors with less load

RequestRectangles(region)

Continue(region, decompose)

/* other functions visible to other objects */

} /* RectangleManager */

```

Figure 2: The branch office object for data distribution of rectangles.

these phases.

#### 3.1 Data Distribution

In order to effect proper load distribution for parallel circuit extraction, it is important to ensure balanced data distribution. This needs to be accomplished with minimum overhead during data distribution, and at the same time, it must not complicate the merge phase of the circuit algorithm which combines the results computed for each of the partitions of the circuit, as was the case in the point-based partitioning in the PACE algorithm [4].

The distribution of rectangles is implemented using the branch office object outlined in Figure

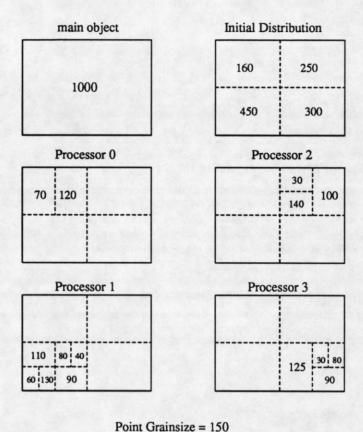

Figure 3: A simple example illustrating the data distribution for 4 processors. Note that the number of rectangles in an region is smaller than the sum of the rectangles in its 2 subregions since border rectangles are given to both subregions.

2. It also provides access routines to the distributed data. These routines are used as necessary by the dynamically created objects in the system. In Figure 2, the C-code associated with the Init entry point is executed on every processor upon creation of the branch office. A main object reads in the circuit description and partitions the rectangles area-wise into n partitions, where n is the number of available processors. The partitions are sent to the respective processors to the ReceivePartition entry point. The rectangles are locally partitioned further based on a user-defined threshold and the local load is broadcast to the ReceiveRectLoad entry point of the sibling branch offices on the other processors. The branch offices then determine the best distribution of the local partitions across the available processors. Some of the processors with surplus rectangles tag some

of their local regions as those to be processed by other processors. No movement of rectangles takes place at this point. We discuss how this is accomplished below in more detail.

Initially, the circuit is partitioned using an area-based partitioning scheme so as to assign a region of the circuit to every processor. The rectangles comprising the circuit from a file are read in and sent to the processor owning the circuit partitions to which they belong. A processor will also get all the rectangles that touch a border of the circuit region it owns. These rectangles are sent in several 'rectangle' messages to overlap the processing of these rectangles with the reading in of the input.

Upon initialization, on each processor, a hash table is created to store the data distribution. This table is used to store all the nodes resulting from the initial area-partitioning nodes, together with local nodes resulting from the local point-based partitioning in the parallel circuit partition tree (see Figure 3). Each processor also initialize two counts: a count of the number of 'rectangle' messages it expects to receive (init-msg-count = 1) and a count of the number of messages it expects to receive from the other processors indicating the local point-based distribution on the respective processors: (rect-load-count = num-processors -1). Every message except the last sent to the processors as the circuit is being read in carries a send-count field = zero. In the last message, however, the send-count field is set to number of messages sent + 1. Upon receipt of a message, a processor increments its init-msg-count by 1 and decrements it by send-count. This ensures that init-msg-count is zero if and only if all the messages have arrived, irrespective of the order of arrival. The use of rect-load-count is described below.

As and when the messages are received, the rectangles in the message are inserted into a partition tree. The root of the partition tree on every processor is the entire region owned by the processor. Initially, the root of the tree is the only node in the tree. Rectangles are only stored at the leaf nodes of this tree. When the number of rectangles at a leaf node L of the tree exceed a user defined limit (called point grain size), the region represented by L is split into two. Two leaf nodes  $L_1$  and  $L_2$  are created as children of L, and the rectangles stored at L are distributed between  $L_1$  and  $L_2$  (the rectangles on the border are given to both regions). Thus, when all the rectangles from the main process have been received and processed, every leaf node has  $\leq point$  grain size rectangles. One triple (region, penum, rectangle-list) for every node in the partition tree

is stored in the local data-distribution hash table. (The center of the region is used as the key to index the hash table.). This constitutes the *local* phase of data distribution.

Once all the rectangles bound for a processor p have been received and processed, a message containing the *number* of rectangles owned by p is broadcast to the other processors. This number typically exceeds the number of rectangles received when the circuit was read in because it accounts for the duplication of "border" rectangles. Note that no rectangles are sent across processor boundaries at this time. Each processor will receive *num-processors* -1 such messages. The local rect-load-count field is used to check the arrival of all such messages at a given processor. When all these messages arrive, processors having more rectangles than the average assign some leaf regions to lean processors. This is done by accessing the local hash table and changing the *penum* field in the triple (region, penum, rectangle-list) appropriately. The rectangles are not sent to the lean processors at this stage. Moreover, Care is taken to ensure that several surplus processors do not all assign rectangles to a same lean processor but distribute it across the lean processors uniformly<sup>4</sup>.

After a processor receives its rectangles, creates its local partition tree, and broadcasts the number of rectangles to other processors, it is ready to begin the decomposition phase (Section 3.2). It does *not* wait for the receipt of all *rect-load-count* messages from other processors.

The hash table, the partition tree and count information is all managed by a local data object on each processor. These processes together provide a form of distributed data abstraction to the processes created during the execution of the circuit extractor (see below).

## 3.2 The Decomposition Phase

Once all the rectangles have been read in and sent to the respective processors, an object responsible for the entire circuit area is created. The object is named the *CircuitExtractor* object in Figure 4.

In Figure 4, an outline of the object used to perform circuit extraction is shown. Briefly, decomposition continues until the user-defined threshold is reached. This decomposition and the corresponding creation of objects mirrors the data partitioning performed by the branch office. When decomposition stops, the *RequestRectangles* function of the local branch office is queried for the rectangles in the specified region, with a "reply-to" entry point = *ReceiveRectangles*. If these

<sup>&</sup>lt;sup>4</sup>No additional messages are sent to accomplish this. Each processor runs a local deterministic algorithm on the periodic load information received from the other processors.

```

chare CircuitExtractor {

LocalDataType data;

ObjectIDType parentid;

int

numchildmsgs;

*firstchildmsg;

BorderMsg

entry Decompose: (message CurrentRegion *msg)

If ( LoadManager. Continue(msg->region, &decompose))

If (decompose)

Divide msg->region into two equal regions by bisecting its longer sides

Create 2 CurrentRegion messages to represent these regions

CreateChare(Decompose@CircuitExtractor, msg1, pe1)

CreateChare(Decompose@CircuitExtractor, msg2, pe2)

Else

parentid = msg->objectid; numchildmsgs = 0;

LoadManager. RequestRectangles(msg->region);

entry Receive Rectangles: (message Region Rectangles *msg)

ConstructLocalRectangleLists( msg->rectangles, data );

Identify Local Connected Nets netlist and Transistors tranlist

ProcessTransistors(tranlist, &bordertranlist, &localtranresults, data);

ProcessNets(netlist, &bordernetlist, &localnetresults, data);

Report local transistors

Insert complete nets in netlist in LoadManager:localnets

Create a message bordermsg containing all border net and transistor info.

SendMsg(CircuitExtractor@MergeRegions, bordermsg, parentid);

entry MergeRegions: (message BorderMsg *msg)

numchildmsgs = numchildmsgs + 1;

If (numchildmsgs == 2) /* both messages received */

MergeRegions( firstmsg, msg, data);

Identify Local Connected Nets netlist and Transistors tranlist

Process Transistors (transist, &bordertransist, &localtranresults, data);

ProcessNets(netlist, &bordernetlist, &localnetresults, data);

Report local transistors

Insert complete nets in netlist in LoadManager:localnets

Create a message bordermsq containing all border net and transistor info.

SendMsg(CircuitExtractor@MergeRegions, bordermsg, parentid);

Else

firstchildmsg = msg;

}

```

Figure 4: The object that implements the circuit extraction algorithm. Some liberties have been taken with notation for ease of exposition.

Load balancing: leaf sent from PE 1 to PE 2

| Initial Distribution:     | Final Distribution:      |

|---------------------------|--------------------------|

| PE 0: 190 rectangles -134 | PE 0: 300 rectangles -24 |

| PE 1: 510 rectangles +510 | PE 1: 340 rectangles +14 |

| PE 2: 270 rectangles -54  | PE 2: 330 rectangles +6  |

| PE 3: 325 rectangles +1   | PE 3: 325 rectangles +1  |

average: 324 rectangles Grain size = 150Tolerance -50 to +50

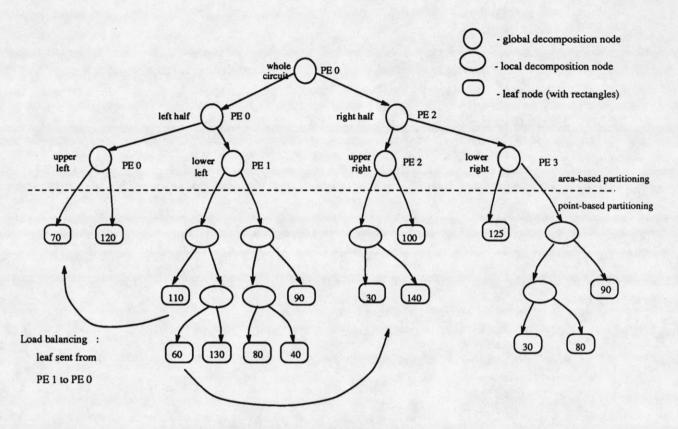

Figure 5: The dynamic redistribution of objects to load balance the rectangles in Figure 3. Each node in this decomposition tree represents an extractor object.

rectangles are not available locally, the local branch office first determines the owner processor for the requested rectangles. It then sends a message requesting the rectangles to the SendRectangles entry point of its sibling branch office owning the rectangles. The owner branch office sends the requested rectangles to the RequestRectangles entry point of the requesting object.

A CircuitExtractor object queries the local branch office to determine whether further decomposition is necessary. This is determined as follows. If the region owned by the Circuitextractor object (its current region) is not present in the local hash table, further decomposition is deemed necessary. If the current region falls within the circuit region owned by the local processor, it is necessary to wait until the local data partitioning phase is complete. This is accomplished with a do not continue response. The querying process suspends and relinquishes the processor upon receiving a do not continue response. When local data partitioning is complete, these processes are woken up and this query is retried. If further decomposition is required, the hash table provides the processors on which the child process instances are to be created. Recall that the destination of leaf processes may change due to distribution of rectangles as explained in Section 3.1. Non leaf processes resulting from the initial area-based partitioning are assigned processors statically. A non-leaf processes resulting from point-based partitioning is created on the same processor on which its parent resides (see Figure 5).

If the information necessary to answer the query is available locally, the data distribution hash table is checked for an entry corresponding to the current region. Recall that only hash table entries for leaf nodes in the decomposition tree carry rectangles. Hence, if the entry in the hash table has no rectangles, the process may continue execution, but must decompose the current region further. This is accomplished by dividing the current region into two equal parts by bisecting its longer sides. An instance of the *CircuitExtractor* object is created for each of these regions.

If the current region falls within a region owned by another processor, no further decomposition is necessary since only *leaf* nodes in the decomposition tree may cross processor boundaries for load balancing. The process then requests the rectangles that belong to its current region and relinquishes the processor. The local data process sends the necessary data and wakes up the requesting process. Sometimes, it may be necessary for the local data object to forward the query to a data object on another processor to satisfy the request. In this case, the data object on the

processor owning the rectangles sends the rectangles to the requesting CircuitExtractor object. This is done transparently as far as the requesting CircuitExtractor object is concerned.

The requesting CircuitExtractor object is now primed for local processing. Due to the large sizes of the messages exchanged between processes, processes created during area-based partitioning (see Figure 5) are mapped onto processors so that a parent CircuitExtractor object and one of its children reside on the same processor.

#### 3.3 The Local Extraction Phase

We first describe the local processing performed with the assumption that all nets and devices computed are completely local to the region. We then discuss how nets and devices touching the border are handled.

The local processing of a region of the circuit is very similar to that employed by the PACE algorithm. To avoid repetition, we describe it very briefly here, emphasizing the differences between the two algorithms. A scan line algorithm is used to determine the local connected components and to identify nets and transistors. This forms the netlist extraction component of the algorithm. The output of this component is a list of devices and a list of nets. A device is described as a collection of device rectangles. For each device, information about the nets connecting to the different terminals of the device is also computed. A net is also described as a collection of rectangles. For each net, information about devices that connect to the net is computed.

For parameter extraction, we use the resistance-capacitance model used in HPEX [23]. The resistance of a net are converted into a horizontally maximal non overlapping form. This is also accomplished by a scan line algorithm. This will produce a unique representation of the net. The horizontally long rectangles are then combined in the vertical direction. Two rectangles that are sufficiently longer in the x direction than the y direction are combined vertically if they abut on their horizontal edges. Once this is done, for every rectangle R that is longer in one direction than other rectangles abutting it, R's larger side is cut at the point of intersection with the abutting rectangles. Two overlapping rectangles resulting from such intersections are merged.

Two rectangles are said to be electrically connected if they abut each other. A rectangle that connects to only one other rectangle, or at least three or more rectangles is defined to be a knot.

Rectangles associated with the terminals of devices are defined to be *ports*. The remaining rectangles all have exactly two connections each and are defined to be *branch* rectangles. Every knot and port is assigned a globally unique number which identifies a point of connection in the circuit. A net can be thought of as an undirected graph where the knots and ports are nodes that are connected to each other by edges which represent a chain of one or more branch rectangles.

Resistance calculations are then performed for every edge in the graph representing a net. The contribution of the knots and ports are also factored into the calculations. Capacitance calculation is also performed at the same time. The capacitance of each of the knots and ports is first determined. The capacitance of each of each edge in the graph is computed by adding the contributions of all the branch rectangles on the edge. This capacitance is equally divided between the two end points. The result of this phase is a distributed RC network for each net. Currently, we do not perform a node reduction phase on the resulting network as is done in HPEX [23], but these features can be included easily.

For parallel execution, the maximally connected nets and devices are identified as described above. Following that, they are subject to the horizontal and vertical transformations and unique identification of knots and ports. However, both nets and devices may touch a border. All knots touching a border are marked as border rectangles. Rectangles abutting an incomplete transistor are also treated like border rectangles. Furthermore, for every edge in the graph representing a net, if any rectangle on the edge (including the end points) touches the border, all the rectangles including the end points are marked. Only the marked regions of a net will be sent to a parent process during the merge phase. The resistances and capacitances are computed locally for the non-marked regions of the net and the rectangles are then discarded.

Resistance and capacitance calculations are computed as before with some exceptions. (a) Capacitance is not computed for marked rectangles. (b) Resistance is not computed for marked rectangles. (c) Resistances and capacitances are computed for edges that are not marked even if one or both of their end points are marked. In this case, the computed capacitance is divided equally between the end points as described earlier. Resistances are reported immediately using the unique node identifiers assigned to their end points. Marked end points carry the partially computed capacitances and their unique node identifiers up the decomposition tree until they

become unmarked. The results are reported at this stage. Note that that same unique identifiers will be used to report the capacitances. (d) Knot rectangles that are marked but do not touch the border are tagged as knots to avoid being identified as branch rectangles in an ancestor region.

The marked regions of a net together with partially computed resistances and capacitances at the knots not touching a border are sent up to the parent process. The computed values for the unmarked regions of a net are reported with a globally unique number identifying the net. However, if the reported results correspond to an incomplete net, the results are tagged as incomplete.

Local transistors, like local nets, pose no problem. Local transistors are reported as soon as they are encountered and processed. Border transistors, however, can pose potential problems. For each complete transistor, unique node numbers identify the gate, source and drain terminals. One node is created to represent the gate of the transistor and is tagged as a poly port. Two additional nodes are created for the source and drain nets of a transistor and tagged as diffusion ports. A rectangle bounding the channel rectangles of the transistor is used to represent the diffusion ports. This guarantees that the relevant sections of the source and drain nets will be marked as border rectangles if the transistor touches the border. The terminals of a transistor are only determined once a transistor is complete. The channel rectangles of an incomplete transistor are sent up to the parent process together with references to all nets abutting it. Unlike nets, device extraction results are only reported once the device is complete.

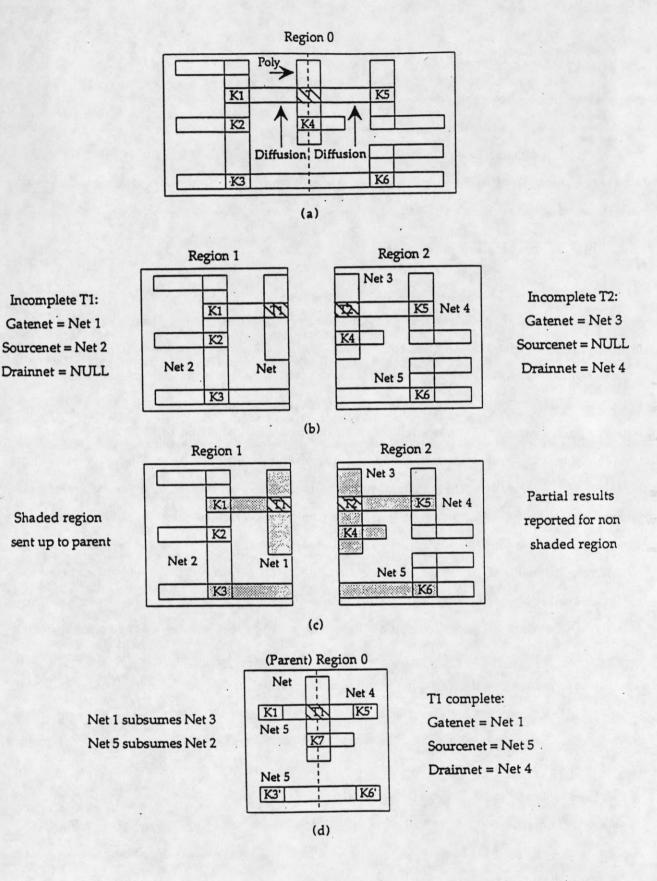

We illustrate this with the help of the simple example circuit in Figure 6. Figure 6(a) describes an entire circuit in a region  $R_0$  in a form ready for parameter extraction if executed on one processor. We consider the case where it has been divided into two regions  $R_1$  and  $R_2$  (Figure 6(b)) which are processed by two processors. Figure 6(c) describes the state after local netlist and device extraction. Transistors  $T_1$  and  $T_2$  are recognized as incomplete on their respective processors. The determination of the source and drain nets is deferred until the transistor becomes complete. The regions of the nets that are connected to the common border are marked as shown. The resistance and capacitances for the unmarked regions are then computed. For example, the capacitance computed and lumped at knot  $K_2$  is reported (as belonging to net 2). The resistances between  $K_1$  and  $K_2$ ,  $K_2$  and  $K_3$  etc. are also reported. The partial capacitances computed at knots  $K_1$ ,  $K_3$ ,  $K_5$  and  $K_6$  together with the node identifiers assigned to them are sent up to the parent process

Figure 6: A simple example illustrating the behavior of the parallel circuit extraction algorithm.

responsible for  $R_0$ . No resistance or capacitance values are computed for knot  $K_4$ .

As soon as a leaf process completes local geometric extraction, it processes the local complete transistors, deposits the local complete nets in a *local nets* list in the local data object, and sends a message to its parent containing the border nets and transistors. It then terminates and frees up any allocated memory.

### 3.4 The Merge Phase

At the leaf processes of the circuit decomposition tree, four lists of border rectangles are created, one for each border. For efficiency, these rectangles are chopped to line segments along the border. Overlapping line segments are then combined to reduce the number of line segments sent up to a parent process. Note that two adjacent regions will have the same set of line segments on the common border since rectangles touching the common border are made available to both the regions. These line segments point to the net or device that they belong to.

When a non-leaf process in the decomposition tree receives one message each from its children, it is ready to begin processing them. The common border between the two child regions is determined and the set of line segments corresponding to the respective borders of the child regions are sorted. The nets or devices corresponding to the same line segment in the two lists are merged.

Merging two nets will result in one net subsuming another. However, the child process may have reported results corresponding to local parts of these nets using the globally unique identifiers given to these nets during the local extraction. Thus, the resulting net creates a list of net identifiers of all nets it subsumes. A net may subsume more than one other net during the merge process. This suggests that a list of merged net identifiers need to be created in the general case. It is also possible for two nets, that have subsumed one or more nets each, to be merged. This means that corresponding list of merged net identifiers also need to be combined when two nets are merged. Once the merge operation is completed at an internal node in the decomposition tree, for every net N resulting from the merge, the list of nets subsumed by N is reported.

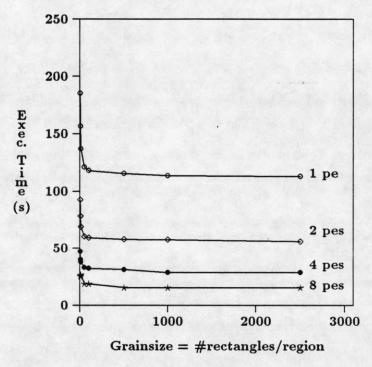

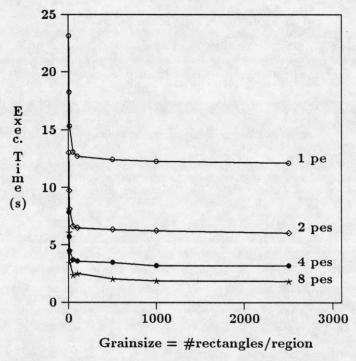

For transistors, the list of channel rectangles of the transistors being merged are combined and carried by the resulting transistor. As mentioned during the local extraction phase, it is necessary to keep the information relating to the connecting nets consistent. Thus, in Figure 6, when Net 1