# MULTIPLE FAULT DIAGNOSIS IN COMBINATIONAL NETWORKS

CHARLES WEI-YUAN CHA

UNIVERSITY OF ILLINOIS - URBANA, ILLINOIS

# MULTIPLE FAULT DIAGNOSIS IN COMBINATIONAL NETWORKS

by

#### CHARLES WEI-YUAN CHA

This work was supported in part by the Joint Services Electronics Program (U.S. Army, U.S. Navy and U.S. Air Force) under contract DAABO7-72-C-0259.

Reproduction in whole or in part is permitted for any purpose of the United States Government.

Approved for public release. Distribution unlimited.

# MULTIPLE FAULT DIAGNOSIS IN COMBINATIONAL NETWORKS

BY

#### CHARLES WEI-YUAN CHA

B.S., New Asia College, 1968 M.S., University of Illinois, 1970

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Science in the Graduate College of the University of Illinois at Urbana-Champaign, 1974

Thesis Advisor: Professor Gernot A. Metze

Urbana, Illinois

## MULTIPLE FAULT DIAGNOSIS IN COMBINATIONAL NETWORKS

Charles Wei-yuan Cha, Ph.D.

Coordinated Science Laboratory and

Department of Computer Science

University of Illinois at Urbana-Champaign, 1974

A new concept, the prime fault, is introduced for the study of multiple fault diagnosis in combinational logic networks. It is shown that every multiple fault in a network can be represented by a funcationally equivalent fault with prime faults as its only components. The use of prime faults greatly simplifies multiple fault analysis and test generation.

Also, masking faults for a given fault under a given test are defined. The conditions under which fault masking can occur are examined in detail. These conditions lead to an efficient method for generating a locally optimal test for a given prime fault.

With the above two new concepts, an efficient algorithm to generate a multiple fault detection test set for any combinational circuit has been developed. It not only will generate the multiple fault detection test set for an irredundant network; it also pinpoints any redundancy in a redundant circuit.

Bounds on the number of tests in the multiple fault detection test set are also found. The upper bound is the number of prime faults. This leads to a design principle, that is, a circuit should be designed with a minimum number of fanouts in order to yield a minimum number of tests in the multiple fault detection test set. A network designed according to this principle can be easily diagnosed.

#### ACKNOWLEDGMENT

The author is greatly indebted to his advisor, Professor Gernot Metze, for his inspiring guidance, priceless discussions and constant encouragement in the course of the research presented here.

The author wishes to thank the members of the Digital Systems Group of the Coordinated Science Laboratory and particularly Professor E. S. Davidson, Mr. James Smith, and Mr. Trevor Mudge for many useful discussions.

The support extended to the author during the past two years by the Coordinated Science Laboratory of the University of Illinois is gratefully acknowledged. The assistance of Mrs. Martha Meade and Mrs. Rose Harris in the typing of the manuscript is also greatly appreciated.

Finally, the author is very grateful to his wife Alice and to his parents, Chi-fu and Kwok-Ying Cha, for their love and encouragement throughout all of his school years.

# TABLE OF CONTENTS

| Chapter |                                               |                                                                                                                                        | Page                 |

|---------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.      | INTR                                          | ODUCTION                                                                                                                               | . 1                  |

|         | 1.1<br>1.2<br>1.3                             | Reasons for Studying Fault Diangosis<br>Brief Literature Review                                                                        | . 3                  |

| 2.      | BASI                                          | C TERMS IN FAULT DIAGNOSIS                                                                                                             | . 7                  |

|         | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | Introduction                                                                                                                           | 10<br>10<br>12<br>23 |

| 3.      |                                               | LGORITHM FOR GENERATING A MULTIPLE FAULT TECTION TEST SET                                                                              | 30                   |

|         | 3.1<br>3.2<br>3.3<br>3.4                      | Introduction Prime Faults Test Generation and Fault Masking Main Algorithm for Generating a Multiple Fault Detection Test Set Examples | 30<br>34<br>45       |

| 4.      | SOME                                          | PROPERTIES AND GENERALIZATIONS OF THE ALGORITHM.                                                                                       | 67                   |

|         | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6        | Introduction                                                                                                                           | 67<br>77<br>79<br>80 |

| 5.      | DESI                                          | GN PRINCIPLES                                                                                                                          | 93                   |

|         | 5.1<br>5.2<br>5.3<br>5.4<br>5.5               | Introduction  Some Previous Work on Design Principles  Bounds on the MFTS for the Algorithm  A New Design Rule  Examples               | 94<br>95             |

# TABLE OF CONTENTS (continued)

| Chapter |      |                               | Page  |

|---------|------|-------------------------------|-------|

| 6.      | CONC | LUDING REMARKS                | . 107 |

|         | 6.2  | The Idea Behind the Algorithm | . 108 |

| REFEREN | CES  |                               | , 111 |

| VITA    |      | •••••                         | . 114 |

#### CHAPTER 1

#### INTRODUCTION

# 1.1 Reasons for Studying Fault Diagnosis

"To err is human."

The same applies to all machines including digital computers. Machines will malfunction due to various causes, like component disintegration, wrong connections, power failures, and so on. As years go by, digital computers are getting larger faster and more complex. Nowadays, computers are playing a role almost in every aspect of life---managing paychecks, checking identities, controlling production, monitoring air traffic, and so on. This is just the beginning. The extent of human reliance upon these huge machines has almost become a matter of life and death. A malfunction in a digital computer may cause a great deal of damage, expense or even loss of life. Therefore, it is very important that computers run properly, and this importance will increase considerably with time.

What is fault tolerant computing? It is the ability to execute specified algorithms correctly, regardless of hardware failures and software errors. Basically, the technology of fault tolerant computing encompasses theory and techniques of fault and error detection and correction, modeling, analysis, synthesis, and architecture of fault tolerant systems and their evaluation. Thus the scope of fault tolerant computing is broad. This thesis is mainly concerned with fault diagnosis. A fault diagnostician is concerned with the detection and location of

faults within a digital system. A fault in a circuit is detected if we apply some test to the inputs of the circuit and the outputs of the circuit differ from the correct outputs under the same test.

Digital systems have a large number of digital circuits, which are constructed from two basic circuit types, namely combinational circuits and sequential circuits. A combinational circuit is the more basic logical circuit, and sequential circuits are composed of combinational circuits plus memory. The discussion in this thesis is confined to combinational circuits, unless specified otherwise. In order to diagnose a circuit, one should be able to generate a set of tests. One naive way to generate a test set is to use all the possible input patterns of the circuit. Obviously, this will detect all the detectable faults in the circuit. But, the number of tests will exponentially increase as the number of inputs increases. This effectively excludes the exhaustive method of diagnosis in most cases, except for very small circuits. A good diagnostician should be able to generate an adequate set of tests for a given system and meet the following criteria.

- 1) The test set should be complete. It should detect all the faults under consideration.

- (2) The amount of computation required to generate the test set should not be excessive.

- (3) The size of the test set should be small.

Until now, most algorithms for generating test sets have been concerned with single faults only. They assume the circuit cannot have more than one fault at any given time. This assumption is justifiable

only if testing is frequent enough so that the probability of the occurrence of more than one fault during the interval between tests is negligibly small. The probability of the occurrence of a single physical fault which produces several simultaneous logical faults is also assumed to be negligibly small. These two assumptions are not practical in most cases. For example, the single fault assumption may not be valid for the initial check-out of a circuit. Therefore, multiple fault analysis is justified. The main reason why multiple faults have thus far escaped thorough analysis is the large number of possible multiple faults. There are 3<sup>n</sup> - 1 multiple faults compared to only 2n single faults for a circuit with n lines. For example, a circuit with 40 lines has approximately 10<sup>19</sup> possible multiple faults, but only 80 single faults.

#### 1.2 Brief Literature Review

The most straightforward method for generating a test set for a combinational circuit is the use of a fault table. Each test is listed as a row heading and each fault as a column heading. For each test, there is an indication, in the table, of the faults it detects. Then, a minimal set of tests to detect all the faults can be found in the same way as a set of prime implicants is selected to cover all the minterms of a Boolean function. To guarantee minimality, all possible test patterns must appear in the fault table. Therefore, the application of this method must be limited to very small circuits. Kautz [1], Poage and McCluskey [2], Chang [3] and Powell [4] all describe this method.

Armstrong [5] and Sellers et al. [6] pointed out that by using the so-called Boolean difference, one can find tests for a given fault. However, this method requires a large amount of computation. Hence, it is not practical in most cases.

The method of using sensitized paths, to propagate the fault indication from the fault site to a primary output is very useful. This is the basis of many test generating procedures. Roth [7] formalized this concept and incorporated it into his D-algorithm to generate a test for a given single fault. Although the D-algorithm has its drawbacks, many methods which have been found are modifications of it.

Poage [8] proposed a method for writing the output expression of a digital network that incorporates the network structure. From that expression, a single fault detection test set can be derived by a fault table and a multiple fault detection test set can be derived by first finding some 'critical columns'. This is a very beautiful theoretical result. Unfortunately, practical usage of this method is limited as it takes too much time and effort for even a small circuit.

Schertz [9] proposed the concept of fault collapsing. He combines those faults which are inherently indistinguishable into equivalence classes. Then, the fault behavior of the circuit can be completely characterized by the fault classes. This approach leads to a tremendous reduction in the amount of work required. Schertz and Metze [10] also develop some design methods that simplify the method of detection of multiple faults in certain combinational networks.

Hayes [11] has studied normal NAND networks and examined the

conditions under which fault masking may occur. His study led to ways of determining if a set of tests is a multiple fault test set.

Yau and Tang [12] proposed to generate multiple fault test sets based on the method of Boolean differences. But, their method does not apply to all networks, and for certain multiple faults, reverts to Poage's method, which is known to be impractical.

Bossen and Hong [13] find check points in a circuit to characterize multiple faults. The method they derive is not very complex and computation is much simpler than Poage's method. However, the test set they derive is much larger than the optimal test set.

All the above existing methods are not satisfactory for finding multiple fault test sets for general combinational circuits. But, they have built a good foundation upon which a satisfactory method can be constructed. It is the goal of this thesis to generate a nearly optimal multiple fault test set efficiently for any combinational circuit.

## 1.3 Outline of the Thesis

In Chapter 1, an introduction as to the importance of multiple fault diagnosis is given. Also, the literature on other efforts in this area is reviewed briefly. In Chapter 2, some essential definitions are given. In Chapter 3, the main algorithm for generating a multiple fault detection test set for any combinational network is presented. Some examples are then given, and a comparison is made with other existing algorithms. In Chapter 4, some important theorems concerning the algorithm are proved. In Chapter 5, a new design rule is given which

tends to reduce the maintenance cost. Finally, conclusions and some topics for future research are listed.

#### CHAPTER 2

#### BASIC TERMS IN FAULT DIAGNOSIS

# 2.1 Introduction

In this chapter, various terms such as input test patterns, u-tests, e-tests, co-inputs, kernels or canonical fault representations, fan-outnetworks, masking, and redundancy, which are needed to understand the following chapters, will be defined.

#### 2.2 A Fault Model and Its Representation

The logical model of a switching circuit under consideration is composed of AND, OR, NAND, NOR and NOT gates together with primary input lines, primary output lines, and intermediate lines which connect gates. A fault is any condition in a switching network which results in a change of the logical characteristics of that network. In most cases, the change of the logical characteristics can be logically characterized as certain lines of the network being stuck at logical 0 or at logical 1. This is the reason we are using the concept of the "stuck-at" fault.

<u>Definition 2.1:</u> A stuck-at fault component is some physical fault in a circuit which can be logically specified by saying that certain lines in the network are stuck at a constant logical value.

The line x stuck-at the logical value i will be denoted by x/i or  $x^i$  where i is 0 or 1.

The simplest stuck-at fault is one that affects only one

line and causes that line to be stuck at 0 or 1. We designate this as a single fault.

In contrast, a fault that causes more than one line to be stuck at a logical value will be called a multiple fault.

Also, in this thesis faults are considered to be permanent faults; that is, they do not disappear or change their nature during testing.

#### 2.3 Network Structure

There are two different kinds of network structure of interest here. One is the tree structure and the other is the fan-out structure.

Definition 2.2: A network is called a tree structure network if every primary input line and every gate output line in the network enters at most one gate.

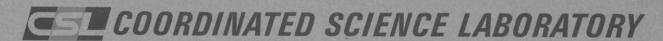

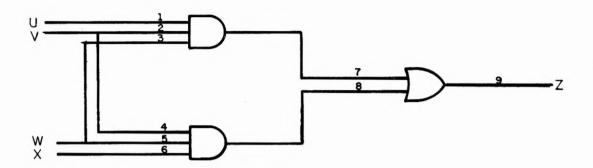

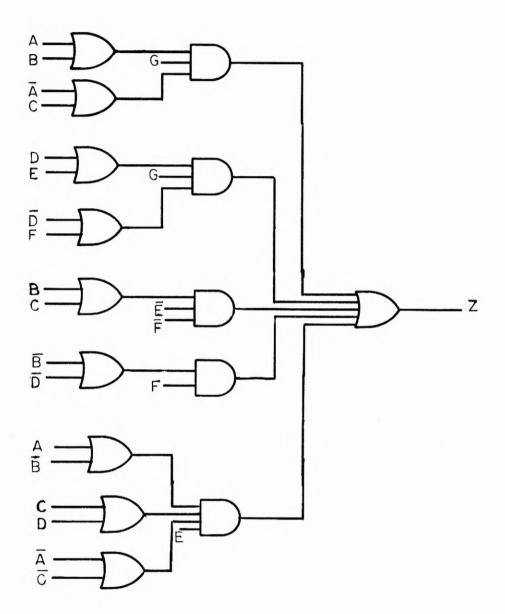

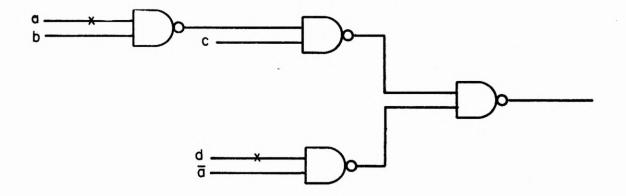

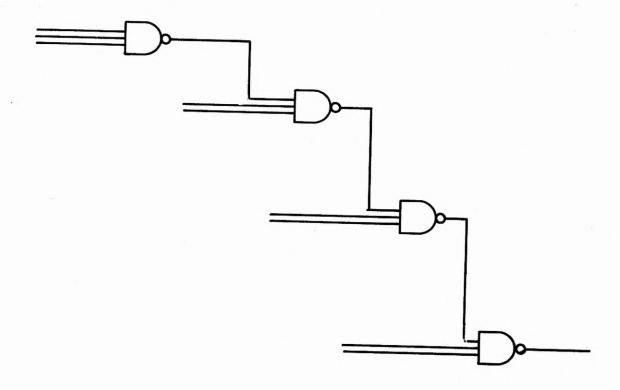

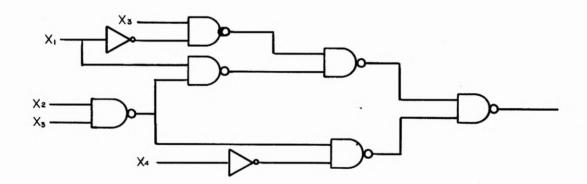

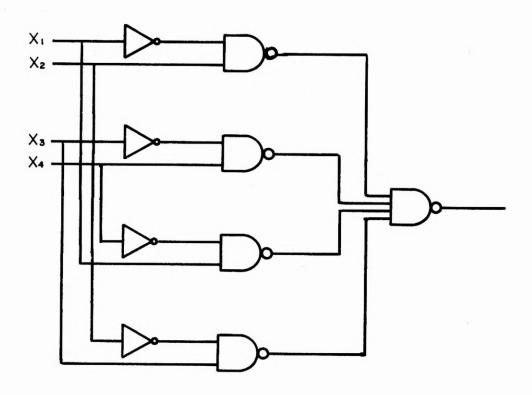

An example is shown in Fig. 2.1 a.

<u>Definition 2.3</u>: A network is called a fan-out network if at least one line in the network enters more than one gate.

An example of a fan-out network is shown in Fig. 2.1 b.

A tree structure network is also called a fan-out-free network. A special class of tree network is a restricted fan-out-free network which is shown in Fig. 4.3. Schertz and Metze [10] have proved that any single fault test set (SFTS) for the restricted fan-out-free network, where primary input fan-out is allowed, is also a multiple fault test set (MFTS). A simple proof of this result will be given in Chapter 4 of this thesis.

Figure 2.1 a) A Fan-out Free Network

Figure 2.1 b) A Fan-out Network

In a fan-out network, the lines which come from the same stem are called branch lines of the fan-out stem. For example, lines 8 and 9 are fan-out branch lines of the stem line 11 in Fig. 2.1 b.

If two or more branch lines of a fan-out point reconverge at a later stage, as lines 8 and 9 do in Fig. 2.1 b, the network is called a reconvergent fan-out network. On the other hand, if fan-out branch lines never reconverge, the network is called a non-reconvergent fan-out network. It is obvious that non-reconvergent fan-out can occur only in multiple output networks. In a single output network, any fan-out is a reconvergent fan-out.

# 2.4 Input Test Pattern

For any gate with inputs  $x_1, x_2, \ldots, x_n$ , there are  $2^n$  different input patterns. In test generation, the input patterns are very important. Hence, we classify the  $2^n$  input test patterns into different categories.

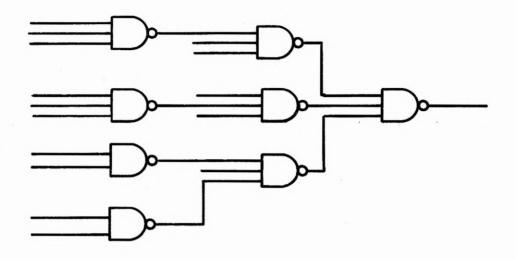

<u>Definition 2.4</u>: For AND and NAND gates, if all the inputs are 1, we call this a u-test input pattern; if all the inputs are 1 except one input which is 0, we call this an e-test input pattern; if more than one input line is 0, we call this an m-test input pattern. An m-test input pattern for which all input lines are 0 is called u-test pattern since its inputs are the complements of the u-test pattern. For OR and NOR gates, 0's and 1's are interchanged in the above.

Fig. 2.2 shows examples of all the different input test patterns for gates with three input lines.

Figure 2.2 Various Input Test Patterns

<u>Definition 2.5</u>: For any gate G with inputs  $x_1, x_2, \ldots, x_n$ , the inputs  $x_1, x_2, \ldots, x_{i-1}, x_{i+1}, \ldots, x_n$  of G are called co-inputs of  $x_i$ .

0 is a dominating input signal for AND and NAND gates, i.e. if any input is 0, then the output will be 0 for AND or 1 for NAND, no matter what the values of the co-inputs of that input are. Similarly, 1 is a dominating input value for OR and NOR gates.

The e-input pattern is the only input pattern which will detect the line  $\mathbf{x}_i$  stuck at 1 (0), where  $\mathbf{x}_i$  has the applied value 0 (1) for AND (OR) or NAND (NOR) gates. The fault  $\mathbf{x}_i/1$  ( $\mathbf{x}_i/0$ ) can only be sensitized through the gate with this input pattern. If the test input for a gate G is an m-test pattern, there is more than one dominating signal on the input leads. In order for any sensitized path to pass through a gate G with an m-test input pattern, the test must sensitize all the input lines of G that have dominating values on them. In other words, the gate with an m-test pattern is less sensitive than under an e-test input pattern. Therefore, the more dominating values on the test inputs, the less sensitive the gate is. This is why the  $\mathbf{u}$ -test pattern, which has all dominating values on its input lines, is also called the optimal desensitizing input pattern. This is a very useful concept in test generation, as we shall see later.

# 2.5 Fault Relations

If two faults  ${\bf F}_1$  and  ${\bf F}_2$  in a network N are present at the same time, we will have a fault  ${\bf F}_3$  that is composed of  ${\bf F}_1$  and  ${\bf F}_2$ . We call this composition on the set of faults 'concatenation'.

<u>Definition 2.6</u>: Let  $\mathbf{F}_1$  and  $\mathbf{F}_2$  be two stuck-at faults. The concatenation of  $\mathbf{F}_1$  and  $\mathbf{F}_2$  is defined by

$$F_3 = F_1 \cdot F_2$$

where  $\mathbf{F}_3$  is the union of the sets of component faults comprising  $\mathbf{F}_1$  and  $\mathbf{F}_2$ , and the union of these component faults, in fact, constitutes a multiple stuck-at fault if they are defined.

As we know, a line cannot be stuck-at-1 and stuck-at-0 at the same time. Hence, if  $\mathbf{F}_1$  has the component i/1 and  $\mathbf{F}_2$  has the component i/0, then the concatenation  $\mathbf{F}_1$  ·  $\mathbf{F}_2$  is undefined.

The set of faults  $\mathcal{F}$  in a network N under the operation of concatenation forms a commutative, regular semi-groupoid [14].

<u>Definition 2.7</u>: A fault  $F_1$  in N dominates a fault  $F_2$  in N if every test t of N that detects  $F_1$  also detects  $F_2$ .

For a network N with the output function Z, we denote by  $Z_N$  the output function of the fault-free network N. The output function may change if the network is under some fault condition F; we denote by  $Z_N[F]$  the output of network N under fault F.

<u>Definition 2.8</u>: Two faults  $F_1$  and  $F_2$  of the same network N are called functionally equivalent if  $Z_N[F_1] = Z_N[F_2]$  for any input to N. We denote this by  $F_1 \cong F_2$ .

Theorem 2.1: Two faults  $F_1$  and  $F_2$  are functionally equivalent if and only if  $F_1$  dominates  $F_2$  and  $F_2$  dominates  $F_1$ .

$\begin{array}{lll} \underline{\text{Proof:}} & \text{If } \textbf{F}_1 \cong \textbf{F}_2, \text{ then } \textbf{Z}_{\textbf{N}}[\textbf{F}_1] = \textbf{Z}_{\textbf{N}}[\textbf{F}_2], \text{ so every test which detects } \textbf{F}_1 \\ \text{will detect } \textbf{F}_2 \text{ and vice versa.} & \text{If } \textbf{F}_1 \text{ dominates } \textbf{F}_2, \text{ every test that} \\ \text{detects } \textbf{F}_1 \text{ also detects } \textbf{F}_2 \text{.} & \text{Similarly, if } \textbf{F}_2 \text{ dominates } \textbf{F}_1, \text{ every test} \\ \end{array}$

that detects  $\mathbf{F}_2$  also detects  $\mathbf{F}_1$ . Also, all tests that do not detect  $\mathbf{F}_1$  do not detect  $\mathbf{F}_2$  and vice versa. Therefore, for any test, the output functions of the network N under Fault  $\mathbf{F}_1$  and  $\mathbf{F}_2$  are the same. By definition  $\mathbf{F}_1 \cong \mathbf{F}_2$ .

Q.E.D.

For a multiple fault, if the fault contains components both on inputs and outputs of some gate, then the output function of the network is affected by the fault on the output line only, as the input line fault is covered by the output line fault. This leads to the following definition.

<u>Definition 2.9</u>: A fault  $F_1$  is an m-covering fault of another fault  $F_2$  if the presence of  $F_2$  together with  $F_1$  affects the network N in the same way as  $F_1$  does alone i.e.  $Z_N[F_1] = Z_N[F_1 \cdot F_2]$ . We denote this by  $F_1 \supseteq F_2$ .

<u>Definition 2.10</u>: Let F be a fault and  $F_1$ ,  $F_2$  be two subsets of F.

- If (1)  $F = F_1 \cdot F_2$

- (2)  $F_1 \supseteq F_2$ , i.e.  $F_1$  m-covers  $F_2$ .

- (3)  $F_1$  is the subset with fewest components which meet conditions

- (1) and (2), then, the fault  $F_1$  is said to be a kernel of the fault F.

For any multiple fault F, if  $F_1$  is the kernel of F, we will have  $Z_N[F] = Z_N[F_1]$ . Since  $F_1$  m-covers  $F_2(=F-F_1)$ , we can neglect the subfault  $F_2$  completely and need to consider only those fault components in  $F_1$ . Therefore, we can always use the kernel  $F_1$  of a multiple fault F to represent the fault F. We also call  $F_1$  the canonical fault representation of F.

For fault m-covering, we also have the following theorem.

Theorem 2.2: If  $F_1$  m-covers  $F_2$  and  $F_2$  also m-covers  $F_1$ , then  $F_1 \cong F_2$ .

$\underline{ \text{Proof:}} \quad \textbf{F}_1 \text{ m-covers } \textbf{F}_2 \quad \Rightarrow \quad \textbf{Z}_{\textbf{N}} [\textbf{F}_1] \ = \ \textbf{Z}_{\textbf{N}} [\textbf{F}_1 \textbf{F}_2] \text{.}$

$F_2$  m-covers  $F_1 \Rightarrow Z_N[F_2] = Z_N[F_2F_1]$ .

Since the set of faults forms a commutative semi-groupoid,  $F_1F_2 = F_2 \cdot F_1 \ \text{if they are defined.}$

Therefore,  $\mathbf{Z_N}[\mathbf{F_1F_2}] = \mathbf{Z_N}[\mathbf{F_2F_1}] \Rightarrow \mathbf{Z_N}[\mathbf{F_1}] = \mathbf{Z_N}[\mathbf{F_2}]$ . So, by definition,  $\mathbf{F_1} \cong \mathbf{F_2}$ .

Q.E.D.

Note--the converse of the above theorem is not true as we can see from the following example.

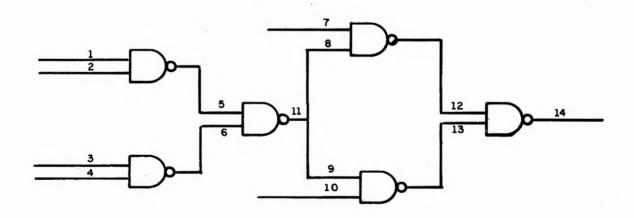

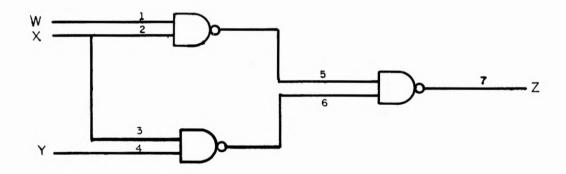

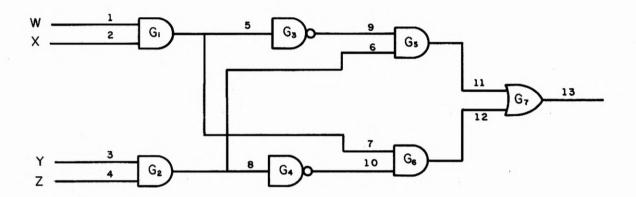

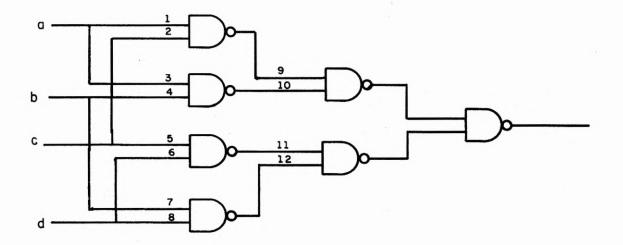

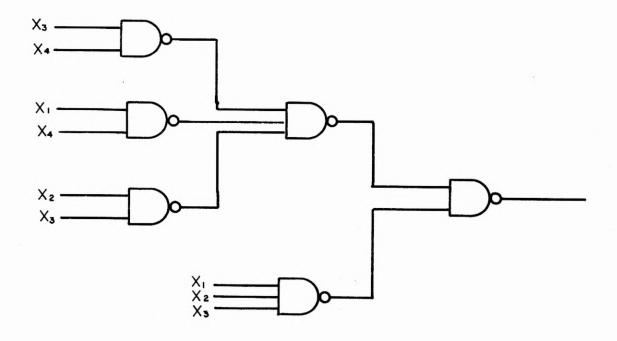

Example 2.1: For Fig. 2.3, let  $F_1 = \{2/0,6/1\}$ ,  $F_2 = \{1/1,5/0\}$ ,  $F_3 = \{7/0\}$ ,  $F_4 = \{1/1\}$ . It is obvious that  $F_3$  m-covers  $F_4$  but neither  $F_3$  dominates  $F_4$  nor  $F_4$  dominates  $F_3$ . This demonstrates the difference between fault dominance and m-covering. It is easily shown that  $Z[F_1] = Z[F_2] = V \cdot W$ . Therefore,  $F_1 \cong F_2$ . But  $Z[F_1F_2] = Z[F_2F_1] = 0$ , so neither  $F_1$  m-covers  $F_2$  nor  $F_2$  m-covers  $F_1$ .

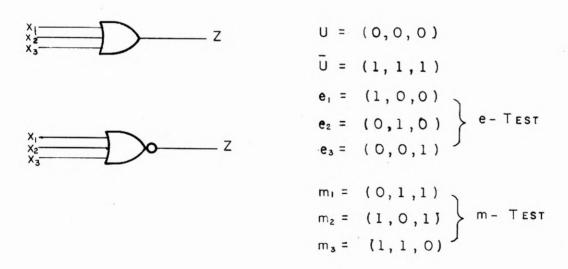

Also, it should be pointed out that functional equivalence is not a congruence relation. For example,  $F_1 \cong F_2$  and  $F_3 \cong F_4$  do not imply  $F_1F_3 \cong F_2F_4$  as can be seen in the following example.

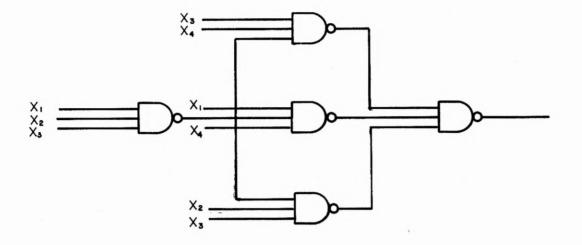

Example 2.2: In Fig. 2.4, let  $F_1 = \{1/1,2/1\}$ ,  $F_2 = \{3/1,4/1\}$ ,  $F_3 = \{6/1\}$ .  $Z_N [F_1] \cong Z_N [F_2] = 1 \Rightarrow F_1 \cong F_2$ .  $F_3 \cong F_3$  since functional equivalence is an equivalence relation. But,  $Z_N [F_1 F_3] = 1$  and  $Z_N [F_2 F_3] = WX \Rightarrow F_1 F_3 \not\cong F_2 F_3$ .

Figure 2.3

Figure 2.4

Since functional equivalence is an equivalence relation, it partitions the set of faults \$\mathcal{F}\$ into equivalence classes. Within any equivalence class, each individual fault affects the output of the network in the same way. Hence, in fault diagnosis we do not have to analyze every individual fault. Instead, we only need to analyze individual equivalence classes. As the number of equivalence classes is far less than the number of individual faults, this will reduce the fault analysis work tremendously. The next obvious question which arises is how all functional equivalence classes are found.

Schertz [15] has a very simple fault collapsing technique.

It is listed in Table 2.2. The 1st and 3rd stages of fault collapsing form functional equivalence classes easily. The 2nd stage collapses dominant faults. Clegg and McCluskey [14] have defined S-structural,

R-structural and functional equivalence. It can be shown that R-structural equivalence is resolved by Schertz's 1st and 3rd stages.

By using fault equivalence classes and kernel representations, we will always choose output lines stuck-at-1 as the fault representation of equivalence classes which consist of all input lines stuck-at-0 and output lines stuck-at-1 for NAND gates. Similarly, we will choose the corresponding stuck-at fault representation for other kinds of gates. Therefore, we will always choose stuck-at-1 faults to represent input line faults for NAND and AND gates and stuck-at-0 faults to represent input line faults for NOR and OR gates when analyzing faults other than faults on the primary outputs and fan-out stems. This immediately reduces the number of faults to be considered by almost a half. In

| Туре        | Description                                                   |

|-------------|---------------------------------------------------------------|

| fanout of 1 | origin sal <=> destination sal origin sa0 <=> destination sa0 |

| AND         | any input sa0 <=> output sa0                                  |

| OR          | any input sal <>> output sal                                  |

| NAND        | any input sa0 <=> output sa1                                  |

| NOR         | any input sal <=> output sa0                                  |

| NOT         | input sal <=> output sa0 input sa0 <=> output sa1             |

a.

| Туре                    | Description                                                          |

|-------------------------|----------------------------------------------------------------------|

| non-reconvergent fanout | any destination sal ⇒ origin sal<br>any destination sa0 ⇒ origin sa0 |

| AND                     | any input sal ⇒ output sal                                           |

| OR                      | any input sa0 ⇒ output sa0                                           |

| NAND                    | any input sa1 ⇒ output sa0                                           |

| NOR                     | any input sa0 ⇒ output sa1                                           |

b.

| Туре   | Description                                                             |

|--------|-------------------------------------------------------------------------|

| fanout | origin sal <=> all destinations sal origin sa0 <=> all destinations sa0 |

| AND    | output sal <=> all inputs sal                                           |

| OR     | output sa0 <=> all inputs sa0                                           |

| NAND   | output sa0 <=> all inputs sal                                           |

| NOR    | output sal <=> all inputs sa0                                           |

c.

Table 2.2

Summary of Fault Collapsing Techniques

addition, the concatenation is always defined since we only choose one kind of stuck-at fault for every line except for the primary output line. NOT gates can be considered as either single-input NAND gates or single-input NOR gates. For uniformity, we consider NOT gates as single-input NAND gates.

The equivalence classes chosen by the above simplified method are good enough for most practical uses, even though the method will miss some equivalence classes, i.e. some equivalence classes may combine into one larger equivalence class as we can see from the following example.

For single faults, there are 12 fault equivalence classes to be considered instead of 20 individual faults.

But, the classes  $\{c_5, c_6, c_8\}$ ;  $\{c_2, c_9\}$ ;  $\{c_3, c_7\}$  and  $\{c_1, c_4\}$  can be combined into single equivalence classes. Actually, we need to form only 7 equivalence classes for single fault analysis.

From the above example, we can see the number of combined equivalence classes is less than the number of equivalence classes that we had initially. Unfortunately, it is not easy to find the minimum number of equivalence classes for all single faults. The above example is a very special case. In most cases the number of equivalence classes

Figure 2.5

formed by the collapsing method is just slightly larger than the minimal number of equivalence classes. The remainder of this section will discuss some relations between functional equivalence classes and R-structural equivalence classes.

Clegg and McCluskey [14] have given necessary and sufficient conditions for two faults to be S-structurally equivalent and R-structurally equivalent. Unfortunately, they failed to give a necessary and sufficient condition for functionally equivalent faults and the functional equivalence relation is the most useful relation in single fault analysis. A necessary and sufficient condition for two faults to be functionally equivalent will be given here. However, Clegg and McCluskey have proved that two faults  $\mathbf{F}_1$  and  $\mathbf{F}_2$  may be functionally equivalent but not R-structurally equivalent in an irredundant network if and only if there exists at least one reconvergent fan-out path. Hence, to find functionally equivalent faults that are not R-structurally equivalent we have to concentrate on reconvergent fan-outs.

Theorem: 2.3: Let  $F_1$  and  $F_2$  be two stuck-at faults in a network N. Then  $F_1$  is functionally equivalent to  $F_2$  if and only if either  $F_1$  and  $F_2$  are R-structurally equivalent or there is reconvergent fan-out in N such that the output at the reconvergent point of the reconvergent fan-out under the presence of  $F_1$  is the same as it is under  $F_2$ .

<u>Proof</u>: Sufficiency--If  $F_1$  and  $F_2$  are R-structurally equivalent they are functionally equivalent. Now, if the outputs at the reconvergent point of the reconvergent fan-out are the same under  $F_1$  and  $F_2$ , both  $F_1$  and  $F_2$  have to be stuck-at faults which occur before the reconvergence

point. We can disregard all the lines and gates before the reconvergent point since  $\mathbf{F}_1$  and  $\mathbf{F}_2$  will produce the same value at the reconvergent point. Consider the reconvergent point as a special input. Then the output of the network will be the same for  $\mathbf{F}_1$  and  $\mathbf{F}_2$ , i.e.  $\mathbf{Z}_N[\mathbf{F}_1] = \mathbf{Z}_N[\mathbf{F}_2]$ . By definition 2.8  $\mathbf{F}_1 \cong \mathbf{F}_2$ .

Necessity: If  $Z_N[F_1] = Z_N[F_2]$ , then if  $F_1$  and  $F_2$  are R-structurally equivalent, the proof is finished. So, assume  $F_1$  is not R-structurally equivalent to  $F_2$ . By the theorem given by Clegg and McCluskey, the network must have a reconvergent fan-out, such that both  $F_1$  and  $F_2$  will affect the reconvergent fan-out. If at the reconvergence point of the reconvergent path the functional value in the presence of  $F_1$  is different from the value in the presence of  $F_2$ , then since the reconvergent point is essential to the primary output,  $Z_N[F_1]$  cannot be equal to  $Z_N[F_2]$ . This contradicts our assumption. Therefore, at the reconvergent point of the reconvergent path, the output must be the same under  $F_1$  as under  $F_2$ .

Q.E.D.

The above theorem gives a criterion which determines if two faults are functionally equivalent. This will reduce the work required to form equivalence classes of single faults.

Although we have the necessary and sufficient condition for two faults to be functionally equivalent, the method suggested by the condition is not as easy to apply as the fault collapsing technique.

Therefore, in most cases, we are content to use the simplified collapsing technique for equivalence classes of all single faults.

To find an SFTS for a circuit, we need to find all the equivalence classes of all single faults. Then, we only need to find a set of tests that will detect every equivalence class instead of individual faults. However, we have some difficulty in finding the minimum number of equivalence classes.

In deriving an MFTS, we don't have to find all the equivalence classes of single faults. We only need to find a small set of faults which can be used to model all the multiple faults. Therefore, for MFTS generation, we don't have the difficulty that we face in SFTS generation. Generating an MFTS is not only more natural, but is somewhat easier than generating an SFTS. We will discuss this property in the next chapter.

#### 2.6 Masking Faults

A test t is said to detect a fault F in a network N if  $\mathbf{Z_N} \neq \mathbf{Z_N}[\text{F}] \text{ under the test t.}$

Generally, a test t detects F and at the same time also detects many other faults. For the purpose of generating an MFTS, we are interested in knowing exactly which faults it detects and which faults it does not detect.

<u>Definition 2.11</u>: A fault  $F_2$  is called a masking fault for  $F_1$  under test t if the test t detects  $F_1$ , but does not detect  $F_1 \cdot F_2$  and  $F_2$  does not  $f_1 \cdot f_2 \cdot f_3 \cdot f_4 \cdot f_4 \cdot f_5 \cdot f_5 \cdot f_5 \cdot f_6 \cdot f_6$

For a given test t which detects F there may or may not exist masking faults. If there are masking faults, then we say t detects F

unconditionally. If there is a set of masking faults for F, denoted by  $\mathbf{S}_{\mathbf{F}}$ , we will say the test t detects F  $\mathbf{S}_{\mathbf{F}}$ -conditionally.

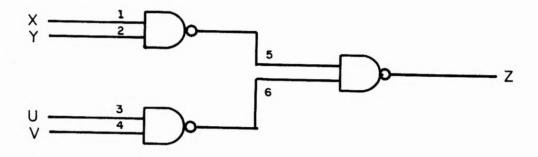

Example 2.4 will illustrate the above terms.

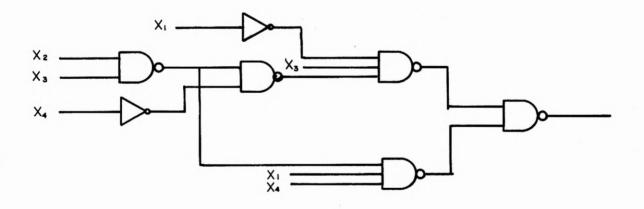

Example 2.4: In Fig. 2.6, the test  $x_1x_2x_3x_4x_5x_6 = 011011$  detects  $x_1/1$  unconditionally. But the test  $x_1x_2x_3x_4x_5x_6 = 011000$  detects  $x_1/1$   $S_F$ -conditionally where  $S_F = \{x_4/1\}$ , since  $x_4/1$  masks  $x_1/1$  under this test.

From the above example, we can see that for a given fault F, different tests which detect F will detect different multiple faults which contain F as a component. This is a very important characteristic in deriving an MFTS. Under what conditions can a fault mask another fault? Hayes [16] stated some criteria in his thesis and this topic will be discussed more in the next chapter.

## 2.7 Redundancy

As pointed out in section 2.5 we are only considering stuckat-1 faults on the inputs of AND and NAND gates and stuck-at-0 faults on the inputs of OR and NOR gates, because other input stuck-at faults are equivalent to their respective output stuck-at faults. Therefore, there is only one fault class which is associated with a given line; this class is called the representative fault class of that line. Representative fault classes will be implicitly used throughout this thesis.

The fault representative of a fault class is associated with a line. There is a strong relation between the lines and their representative faults, i.e. a stuck-at-1 (0) fault is associated with the inputs of AND (OR) and NAND (NOR) gates. We need the following definition.

Figure 2.6

<u>Definition 2.12</u>: We define the fault associated with a set of lines as the fault which occurs when the lines are stuck-at their representative fault class value.

For certain networks, some lines can be stuck at the logical values 0 or 1 without affecting the output of the network, and these lines could therefore be removed from the network without affecting its operation. We will call these lines redundant lines and the circuit a redundant circuit, in the sense that these lines are unnecessary for the logic network.

<u>Definition 2.13</u>: A circuit is single-line redundant if there is some single line that can be removed from the circuit without affecting the logical behavior of the circuit. If a circuit is not single-line redundant we call it single-line irredundant.

Friedman [17] first pointed out that, in redundant circuits, a fault that is originally detectable may become undetectable due to faults on the redundant lines, which are undetectable. Hence, redundancy is very undesirable from a fault diagnosis viewpoint. Though some redundancy like Triple Modular Redundancy (TMR) and some redundant checking circuits are useful for producing higher reliability for a short length of time, unintentional logic design redundancies are a waste of money and are difficult to detect. Therefore, unintentional redundancy is very undesirable in logical design. This leads to an obvious question: how can one find all the redundancies in a network? Before we tackle this question, we give an equivalent, alternative definition of redundancy.

<u>Definition 2.14</u>: A set of lines is redundant if there does not exist a test to detect the fault which is associated with this set of lines.

The two definitions for redundancy are equivalent, since if a line is redundant, then, the output is not sensitive to the value on the redundant line, but, in order to detect the fault on this line, we have to sensitize the fault from that line to the output. If the output is not sensitive to the line, we are unable to detect the fault and vice versa.

With the above definition, we can determine if a circuit is single-line redundant or not by deriving an SFTS for the circuit. If there does not exist an SFTS for the circuit, then the circuit is single-line redundant; otherwise, it is single-line irredundant. Many methods exist for generating an SFTS. Therefore, the problem for detecting single-line redundancy has been solved.

At first glance, one may think that if a circuit is singleline irredundant, it will necessarily be an irredundant circuit.

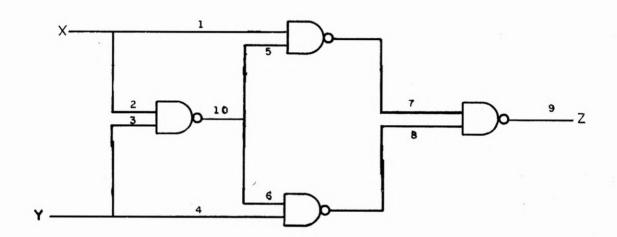

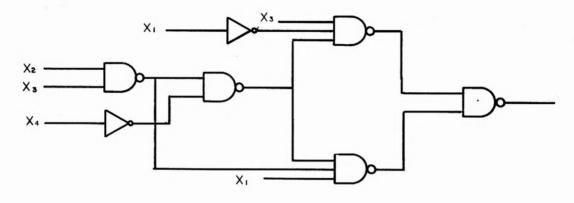

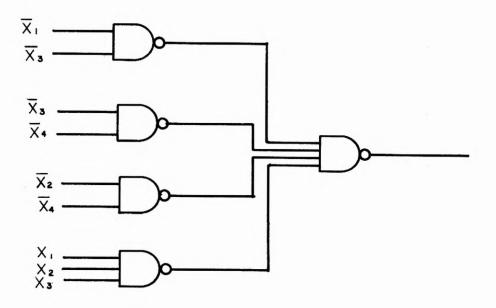

Unfortunately, this is not true. The circuit in Fig. 2.7 is singleline irredundant, but has a 4-line redundancy. Hence, to detect whether

a circuit is redundant is a very difficult job. To verify that a circuit

is multiple-line irredundant it is necessary to first check all single

lines, then every pair, triple, and so on. 2<sup>n</sup> possible redundancies

must be checked. This is practically impossible for even a moderate

circuit. So far the literature does not show a good method to detect

all the redundancies in a circuit. A method which detects all redundancies

in a circuit as a by-product of generating the MFTS for the circuit

Figure 2.7

will be presented.

The example in Fig. 2.7 shows a single-line irredundant circuit which is a four-line redundant circuit. Until now, the existence of a combinational circuit that is single-line irredundant but is two-line or three-line redundant has neither been proved nor disproved. However, for certain circuit configurations we have some theorems [10], [21] that are discussed in Chapter 4.

#### CHAPTER 3

AN ALGORITHM FOR GENERATING A MULTIPLE FAULT DETECTION TEST SET

### 3.1 Introduction

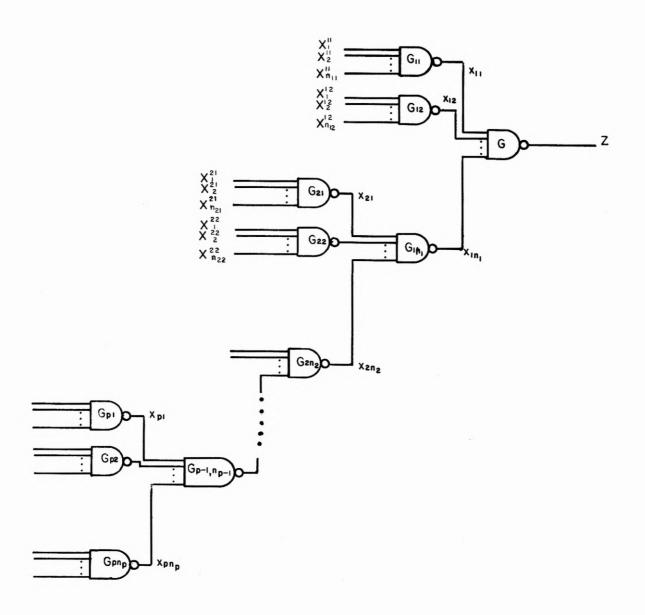

Procedures for generating an SFTS usually involve the use of the D-algorithm [7], Boolean difference [5,6] or some other form of path sensitization method [1,4,11,12]. Some procedures for the generation of MFDTS's have appeared in the literature [2,8,9,11,12,13,25]. However, these procedures are essentially extensions of the standard single-fault approach which differ from it only in that the bookkeeping is considerably more tedious and they tend, therefore, to be very inefficient. As multiple fault detection becomes more important with the advance of large scale integrated circuits, a new look at multiple fault diagnosis is needed. In this chapter, an algorithm for MFDTS generation that is inherently efficient will be developed. First, prime faults are defined and a new path sensitizing technique for generating tests efficiently and for finding the corresponding masking faults is described. Then, the algorithm is summarized. Lastly, some examples to illustrate this algorithm and compare it with other methods are given.

### 3.2 Prime Faults

Freed from the single fault assumption, it becomes possible to represent all the faults in a network by a subset of all the single faults such that any fault in the network will be functionally equivalent to a fault with components in that subset of faults only. Therefore we

<sup>\*</sup> MFDTS = Multiple fault detection test set.

define the set of prime faults as follows.

<u>Definition 3.1</u>: A subset of faults in a network N is called a set of prime faults if for any fault F in N, we can find a functionally equivalent fault  $F^1$  whose components are in the set of prime faults only. In other words  $Z(F) = Z(F^1)$ . Any member of the set of prime faults will be called a prime fault.

<u>Definition 3.2</u>: A gate is called a prime gate if all the input lines of this gate are either primary input lines or branch lines of some fan-out points.

As we are concerned with multiple faults, from now on, whenever we refer to a fault, we mean either a single fault or a multiple fault, unless we specify otherwise. Also, we do not have to consider faults on fan-out stems, because a stuck-at-1 or stuck-at-0 fault at the fan-out stem is just equivalent to the multiple fault with every branch line of the fan-out stuck-at-1 or stuck-at-0. A procedure for finding a set of prime faults is presented as follows.

#### Procedure 1:

- a) Pick all s-a-1 (s-a-0) faults on all the branch lines of all fan-outs that lead to NAND (NOR) or AND (OR) gates.

- Pick all s-a-1 (s-a-0) faults on all the primary input

lines that do not fan-out (if they do, they were already

picked in step (a)) and that lead to NAND (NOR) or AND

(OR) gates.

- c) Pick the s-a-1 (s-a-0) fault on the output lines of prime gates which do not fan-out, where the prime gate is a NAND

(NOR) or OR (AND) gate.

We use PF to denote the set of prime faults generated by Procedure 1.

Theorem 3.1: PF forms a set of prime faults.

<u>Proof</u>: A network can have only two kinds of gates, namely, prime gates and non-prime gates. By Procedure 1 we have a representative for each fault equivalence class for prime gate input lines. For example, if the prime gate is a NAND gate and its output goes to another NAND gate, then we have s-a-1 faults for all the input lines of the prime gate by step (a) and (b). Also we have a s-a-1 fault for the output line of the prime gate by step (c), which is functionally equivalent to any input line of that prime gate s-a-0. For all other types of prime gates which lead to any different gate, the reader can verify for himself that we have chosen representatives for all the input lines of the prime gate s-a-1 and s-a-0.

Now, non-prime gates must have at least one input line that is neither a primary input line nor a branch line of some fan-out. For this line, we can trace back to either a primary input line or a branch line of some fan-out. Hence, for that line to be s-a-1 or s-a-0, we can find a functionally equivalent fault that has components in PF only. If the non-prime gate also has a primary input line or a branch line of some fan-out, it does not change anything.

As we know [13], any multiple fault can be traced back ultimately either to a primary input line or branch line of some fanout. From Procedure 1, we have chosen equivalence classes which include all theses lines s-a-1 and s-a-0. Therefore, any multiple fault can

be represented by some fault or a combination of faults in PF only.

By definition, this is a set of prime faults.

Q.E.D.

A line is called a <u>prime line</u> if it has a prime fault on it.

When we are generating the SFTS for a network, it is

sufficient to pick one representative for each single fault equivalence

class. In dealing with multiple faults, we want one representative

for each multiple fault equivalence class. We need all the prime faults

to make sure the test set will detect any multiple fault. Since function

al equivalence is not a congruence relation as we pointed out in Example

2.2, we cannot delete any single prime fault even though it may be

functionally equivalent to another prime fault.

Example 3.1: See Fig. 2.5 of Chapter 2. By Procedure 1, we will have 1/1, 2/1, 3/1, 4/1, 5/1, 6/1, 7/1, and 8/1 as members of the set PF for that circuit. Although we have  $1/1 \cong 4/1$ ,  $2/1 \cong 8/1$ ,  $3/1 \cong 7/1$  and  $5/1 \cong 6/1$ , neither the set  $S_1 = \{1/1,2/1,3/1,5/1\}$  nor the set  $S_2 = \{4/1,6/1,7/1,8/1\}$  can be deleted from the set PF. We cannot delete 4/1, 6/1, 7/1 and 8/1 from the set PF, because the set  $S_1 = \{1/1,2/1,3/1,5/1\}$  is not a complete set of prime faults. As we can see, the fault  $F = \{6/1,7/1\}$  is not equivalent to the fault  $F_1 = \{3/1,5/1\}$ , because Z(F) = Y and  $Z(F_1) = \bar{X} + Y$ . Therefore,  $S_1$  is not sufficient as a set of prime faults. Similarly,  $S_2$  is not sufficient.

From Procedure 1, we also have the following theorem. Theorem 3.2: The number of prime faults in PF is equal to  $N_1 + N_2 + G_1$  -  $G_2$  where  $N_1$  is the number of primary input lines which do not fan-out,

and the first of the southern all this work is the contract of the contract of

$N_2$  is the total number of all branch lines of all fan-out points,  $G_1$  is the total number of prime gates, and  $G_2$  is the number of prime gates whose output lines fan out. The proof is immediate.

Now, we know how to find a set of prime faults of a network. If we can find a set of tests that will detect all the prime faults and their combinations, then we have an MFDTS. In the next section, we will describe an efficient method for generating a test for a given prime fault together with its corresponding masking faults.

## 3.3 Test Generation and Fault Masking

To find a test for a given prime fault, one can use Boolean difference, path sensitization or some other technique. We tend to use the path sensitization concept for generating the test, because we feel this is the most natural and direct method. However, the path sensitization we will use is different from the widely known D-algorithm. In the D-algorithm, one has to choose one sensitized path at a time and desensitize all others. If a given prime fault needs more than one sensitized path in order to be detectable, one has to exhaust all the single sensitized paths first. Then, one has to sensitize every pair of sensitized paths and so on until a test is found. Therefore, the method is very time-consuming. In order to avoid the above difficulty, we have the following theorem.

Theorem 3.3: In generating a test for a given fault, if more than one path must be sensitized in order to detect that fault, then one can select one path to be sensitized arbitrarily and the chosen sensitized

path will automatically sensitize other paths as needed. That is to say, one never has to choose more than one sensitized path deliberately.

Proof: Suppose in a circuit N, a given fault f requires more than one path to be sensitized in order to detect f. Now, if we choose one sensitized path and deliberately desensitize all the other paths, we will get a contradiction on some line, because sensitizing that one path alone will not allow us to detect f. Therefore, some of the lines we deliberately assigned desensitizing values to in order to desensitize them are dependent on the values of the chosen sensitized path. Let us call the contradictory line a "kill" line.

Now, after we pick a path, in order to assure that the path will be sensitized, we assign all the values on the sensitized path and its co-inputs except those which are the inputs of reconvergent fan-out gates. Now, because of these assigned values on the selected sensitized path the kill line will be forced to have a sensitized value on it. Therefore, the gate with the kill line as one of its inputs will also be sensitized. This will sensitize the other path. Therefore, one never is required to sensitize more than one path deliberately. If another path is needed, it will be automatically sensitized.

Q.E.D.

It is well known that more than one path must be sensitized in order to detect certain faults. Let us use the Schneider example [7] to illustrate Theorem 3.3.

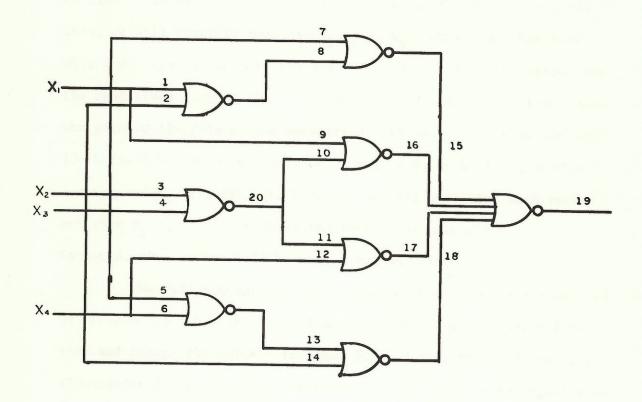

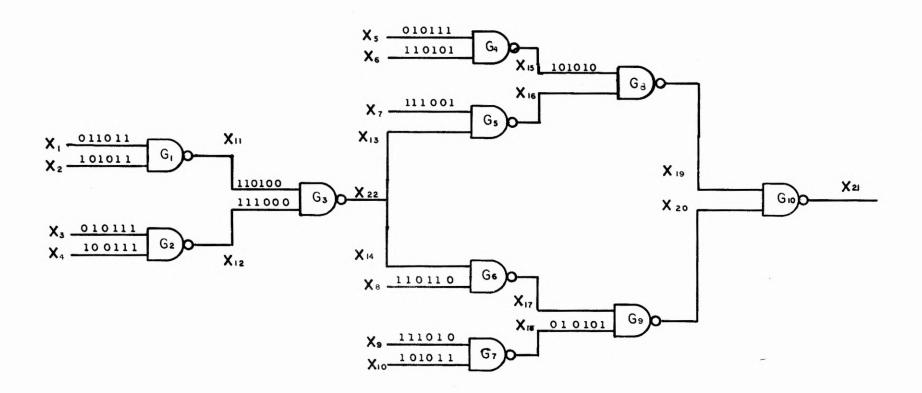

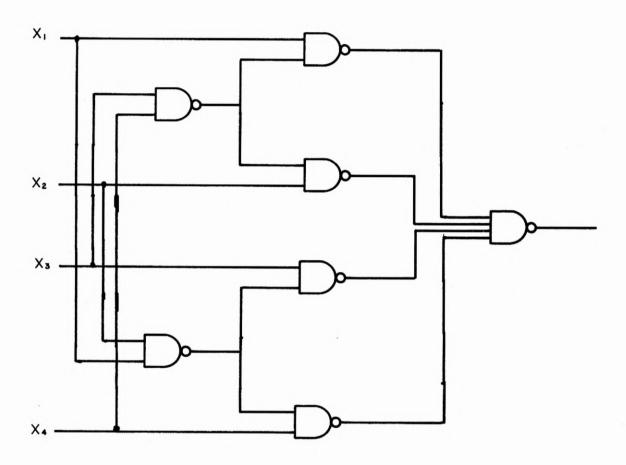

Example 3.2: Fig. 3.1 is the Schneider example. We have to sensitize two paths in order to detect line 20 s-a-0. We use the D-algorithm,

Figure 3.1 Schneider Example

and choose line 20-10-16-19 as a sensitized path first. Therefore, we must apply the value 0 on lines 3, 4, 9, 15, 17, 18 and the value 1 on line 12 to desensitize the path consisting of lines 20-11-17-19. Then, we will generate the test  $\mathbf{x}_1$   $\mathbf{x}_2$   $\mathbf{x}_3$   $\mathbf{x}_4$  = 0001, but this test will force line 18 to have the value 1. This is a contradiction and the sensitized path 20-10-16-19 must be abandoned. Now, if we choose the path 20-11-17-19 as the sensitized path and desensitize the path 20-10-16-19 by applying the value 1 on line 9, we will get another contradiction. Finally, the D-algorithm will sensitize both paths and find  $\mathbf{x}_1$   $\mathbf{x}_2$   $\mathbf{x}_3$   $\mathbf{x}_4$  = 0000 as the test. For networks with more fan-outs, this method will be very time-consuming.

We will now use the new sensitized path technique suggested by Theorem 3.3. We can choose lines 20-10-16-19 as the sensitized path and assign the value 0 to lines 3, 4, 9, 15, 18 and leave line 17 unassigned for the moment as it is an input to a reconvergent fanout gate. Now, since line 18 has the value 0, we must assign line 13 the value 1 because line 14 has the value 0 already due to the value 0 on line 4. In order to have the value 1 on line 13, we have to assign the value 0 to line 5 and line 6. Now, since line 6 has the value 0 so does  $x_4$  and so does line 12. This will sensitize the path 20-11-17-19 automatically without deliberation. Therefore, we get the test 0000 easily. Note here that line 12 is a so-called kill line.

Therefore, in the test generation step, we will use this new path sensitization technique to generate the test; this will avoid the tedious trial and error steps in the D-algorithm.

For a given fault, after generating the partial test that sensitizes a path and will detect the given fault, we have to complete the test. This is the consistency step. Since we want an MFDTS, we must generate a test set that will not only detect all the prime faults, but will also detect all their combinations. Therefore, it is very important to find the set of masking faults for a given fault f under a generated test. Any test that detects a given fault will sensitize the fault from the fault site to the primary output line by at least one sensitized path. Along the sensitized path, we notice that the gates can be divided into two categories.

Definition 3.3: Along a sensitized path, a gate will be called a type 1 gate if it has an e-vector input pattern and the desensitizing value is on the sensitized path. A gate on the sensitized path will be called a type 2 gate if it has a u-vector input pattern. If the fault requires that more than one sensitized path be used to detect it, then at a reconvergent fan-out gate G, more than one input line is on a sensitized path. If all the inputs on sensitized paths have desensitizing values, gate G is called a type 1a gate. If they all have sensitizing values, gate G is called a type 2a gate. Note - the input lines to gate G, which are on sensitized paths, must all have desensitizing values or must all have sensitizing values, otherwise the reconvergent fan-out gate is not sensitized, which is contradictory. Also, we do not consider the gate at the reconvergent fan-out as being on the path of the reconvergent fan-out.

A type 1 subnetwork is a subnetwork that feeds a type 1 gate or type 1a gate and which contains no line that belongs to a sensitized path. A type 2 subnetwork is a subnetwork that feeds a type 2 gate or a type 2a gate and which contains no line that belongs to a sensitized path.

It is easy to show that masking faults in a circuit for a given fault can only mask at type 1 gates or type 1a gates. Therefore, we should apply u-vectors, or optimally desensitizing vectors, to all the gates of a type 1 subnetwork whenever possible. By doing this, we can minimize the number of masking faults for a given fault. On the other hand no masking can occur at a type 2 gate or a type 2a gate. Since they have sensitizing values on all their inputs, they can be part of any sensitized path through any one of their inputs. Therefore, we should try to assign an e-vector input test pattern to all the gates of a type 2 subnetwork whenever possible. By doing this, the test we generate will detect some additional faults. We should always try to let the additional detectable fault be a prime fault. This may reduce the size of the generated MFTS. Now, we are ready to present a procedure which generates a test for a given fault and gives its associated masking faults.

### Procedure 2:

i) For a given prime fault, prime line j s-a-l (s-a-0), apply the value 0 (1) to the prime line j. Also, assign sensitizing values to all of the co-input lines of line j.

- choose a path from line j to the primary output line as a sensitized path. Assign sensitizing values to all the co-input lines of the sensitized path except those input lines at reconvergent fan-out gates.

- iii) Assign values to all the lines which are determined by

(i) and (ii). For example, if in step (i) and (ii) we have assigned the value 0 to the output of a NAND gate, then, this value 0 determines the values on all the input lines of this NAND gate.

- check lines at the reconvergent fan-out gates. If one is already defined due to step (iii) without causing any conflict, we have a type la gate or type 2a gate at the reconvergent fan-out gate. If one line is still undefined, assign the sensitizing value to it. If a line determined by step (iii) always desensitizes the gate at the reconvergent fan-out, then it will desensitize the path.

Therefore, the fault cannot be detected by our chosen path. Choose another path as the sensitized path and go back to step (ii). If we have exhausted all the paths, the fault in question is undetectable. Exit.

- v) This is the consistency step. All lines in the circuit either belong to the sensitized path or are co-inputs to lines on the sensitized path, or belong to type 1 subnetworks or type 2 subnetworks. Previous steps have

defined the values on all lines except some belonging to type 1 subnetworks or type 2 subnetworks. We start from the beginning of the sensitized path, namely the fault site, and assign values to all the lines of the circuit according to the type of subnetwork they belong to.

- Assignment of values to type 1 subnetwork. Masking faults may exist in a type 1 subnetwork. Therefore, we should assign u-vector input patterns to all gates in type 1 subnetworks whenever possible. Since this is not always possible, we must consider a number of cases.

- Case I The type 1 gate which the type 1 subnetwork feeds is not on the path of reconvergent fan-out.

- Case Ia If we can apply u-vector input test patterns to all the gates in this type 1 subnetwork, there is no masking fault in this subnetwork.

- Case Ib If we can not apply u-vector input test patterns to all the gates in this type 1 subnetwork, there are faults that can be masking faults. However, if a fault happens to sensitize a path other than the original sensitized path, such that the newly formed sensitized path passes through a type 2 or a type 2a gate, which is closer to the output than the type 1 gate under consdieration, then that fault will not be a masking fault.

- Case II The type 1 gate which the type 1 subnetwork feeds is on the path of reconvergent fan-out.

- Case IIa The gate at the reconvergent fan-out is not a type 2a gate. If there is a line which needs to be defined, it has a fault that can be a masking fault, unless that fault will sensitize a path other than the original sensitized path such that the newly formed sensitized path passes through a type 2 or a type 2a gate which is closer to the output than the type 1 gate under consideration.

- Case IIb The gate at the reconvergent fan-out is a type 2a gate.

In this case, a masking fault is formed as a combination of one fault for each sensitized path of the reconvergent fan-out, such that every fault will mask one sensitized path.

- Assignment of values to a type 2 subnetwork. For a type 2 subnetwork, we should apply e-vector test input patterns to all the gates whenever possible. If we can, the test will detect additional faults. We should try to make this additional detectable fault a yet undetected prime fault by carefully chosing the e-vector input pattern.

This may reduce the size of the future MFTS.

- vc) If the sensitized path contains a prime line k, which has a prime fault k s-a-i (i is 0 or 1), then we may have masking faults or we may detect additional faults. If

the test assigns the value i on prime line k, then the prime fault k s-a-i will be a masking fault unless the sensitized path passes through a type 2a gate after line k; in that case it will mask only one path of a reconvergent fan-out and the masking fault will be determined as in Case (IIb) of (va). If the test assigns value i on prime line k, then the test will also detect the prime fault k s-a-i, unless the sensitized path passes through a type la gate after line k. In step (v), we derive a test that detects a given prime prime fault k s-a-i and select the prime fault k s-a-i.

- In step (v), we derive a test that detects a given prime fault and which determines the masking faults under the derived test. If the test detects an additional prime fault as in (vb) or (vc), then we should identify that fault's own sensitized path and find its corresponding masking faults just like in (va) and (vc), except we need not assign any values to lines since every line is assigned already. We just examine the new type 1 subnetwork and the new sensitized path as in (va) and (vc) to determine its associated masking faults.

- vii) In the above steps, if we ever encounter some conflict on a certain line, then we should choose a new sensitized path and go back to step (ii); if we have exhausted all the paths we can claim the fault in question is undetectable.

As a convenient way to denote the masking faults for a given prime fault under a generated test, we can use t: f  $\bar{f}_1$   $\bar{f}_2$  ...  $\bar{f}_n$ . That

is, the test t detects f with masking faults  $f_1$ ,  $f_2$ , ...,  $f_n$ , where  $f_i$  can either be a single prime fault or a multiple prime fault.

If the test t detects f and there is no masking fault, then we say the test t detects f complete Fy. That is to say, t will detect any fault that has f as a component of its kernel representation. On the other hand, if there are some masking faults for f under a test t, we say t detects f conditionally.

Now, say  $t_1$  detects  $f_1$   $\tilde{f}_2$  and  $t_2$  detects  $f_2$  completely, then  $t_1$  and  $t_2$  together will also detect  $f_1$ ,  $f_2$  and their combination. Therefore, given a set of tests, we can simply sum their corresponding detectability expressions and use the Boolean algebraic simplification laws to deduce which prime faults the set of tests will detect completely. If we can find a set of tests that will detect all the prime faults completely, then the set of tests is an MFDTS. Therefore, we can use the same Boolean algebraic simplification laws to verify that a set of tests is a MFDTS once we have the complete information for each test, like we get from Procedure 2.

Theorem 3.4: In order for a set of tests to be an MFDTS, there must be at least one test in the set that detects some prime fault completely. Proof: Assume none of the tests detects any prime fault completely. Say  $t_1$  detects  $f_1$  with masking fault  $f_2$ ;  $t_2$  detect  $f_2$  with masking fault  $f_3$ , and so on. Since the number of prime faults is finite, somewhere there will be a loop, say  $f_1$ ,  $f_2$ ,  $f_3$ , ...,  $f_t$ , such that no test in the set can detect  $f_1$   $f_2$   $f_3$  ...  $f_t$ . Therefore the set of tests cannot be an MFDTS.

In order for a set of tests to be an MFDTS, we need at least one test to detect one fault completely as proved by Theorem 3.4.

Usually the more tests which detect prime faults completely, the more likely the set of tests will be an MFDTS. Generally speaking, we try to generate the tests for prime faults with as few masking faults as possible. Procedure 2 does this. Furthermore, Procedure 2 also attempts to detect more than one prime fault with each test in order to reduce the size of the MFDTS. Therefore, any test generated by Procedure 2 is a locally optimal test for the given prime fault under the chosen sensitized path.

In step (va), we decide which faults can be masking faults.

Usually, a masking fault is composed of faults on those lines that

have desensitizing values. If the masking fault is not on a prime line,

we should trace back to its equivalent faults which have prime fault

components only. This can always be done.

# 3.4 Main Algorithm for Generating a Multiple Fault Detection Test Set

With Procedures 1 and 2, we can write our main algorithm rather easily. The algorithm will produce an MFDTS for any irredundant single output combinational network. If the circuit is redundant, the algorithm will point the redundancy out to the designer.

### Main Algorithm:

(1) Pick the set of prime faults by Procedure 1, call it PF. Let  $TS = \emptyset$ .

(2) Choose one prime fault in PF that has not been detected yet. Use Procedure 2 to generate a test that will detect the chosen prime fault together with its masking faults.

If there does not exist a test to detect the given fault go to (7). If a test is found, add the test to TS.

. :

- (3) If not all the prime faults in PF been detected by our generated TS go back to (2).

- (4) If TS detects all prime faults, check TS to see whether it detects all the combinations of all the prime faults.

If it does, TS is an MFDTS. (See Example 3.3 for a method)

- (5) If TS does not detect all the combinations of prime faults, we have a smallest subset of prime faults, called RF, such that TS does not detect a fault that contains RF. In that case, we can pick a fault f in RF and use Procedure 2 to generate another test for f, if possible. For example, we can choose a different sensitized path, etc. The new test should not have masking faults in RF. Then, add the new test to TS if the old test detects some other prime faults that the other members of TS and the new test do not detect; else replace the old test with the new one. For the new TS, go to (4) for new verification. If we cannot find a new test with the above property, continue.

- Pick another fault in RF and repeat step (5). If we have exhausted all the prime faults in RF and are still unsuccessful in finding a new TS such that TS will detect the RF, continue the algorithm.

- (7) If the algorithm enters this step, the circuit is a redundant circuit. The redundant lines will contain those faults that cannot be detected by our generated test set. We should inform the designer that there is redundancy in the circuit.

Note: There are two heuristics which may be used in choosing a prime fault and its sensitized path in step (2) of our main algorithm. The first one is choosing the fault at the highest level (nearest to the primary input) that is still undetected by TS. By using this heuristic, the test will detect other prime faults along the sensitized path if there are any. The other heuristic is to try to use different sensitized paths for different faults, whose prime lines are inputs of the same gate. Since they use different paths, they ususally catch different prime faults that can also be detected by their respective tests. If we use the same sensitized path, since the test derived for one fault is optimal for that path, then for the other fault, we will not gain any new detectability. Though the two heuristics are not necessary, their use is strongly recommended as they will reduce the size of the generated MFDTS in most cases.

## 3.5 Examples

In this section, we use four examples to illustrate our algorithm. We also introduce the table method to verify that a set of tests is an MFDTS.

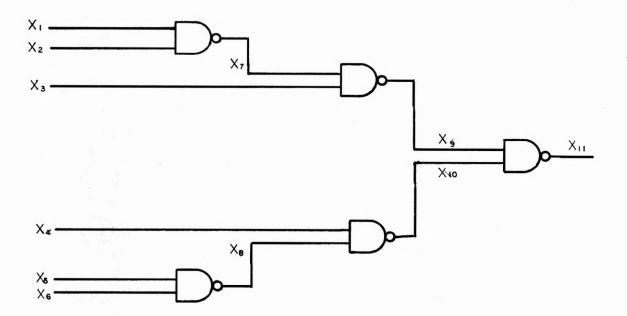

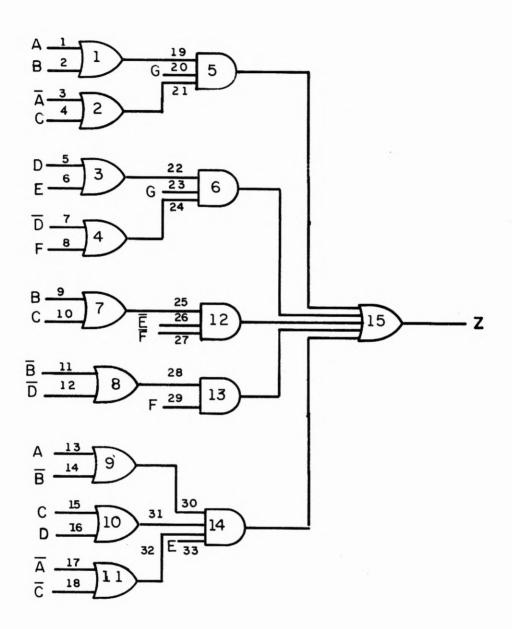

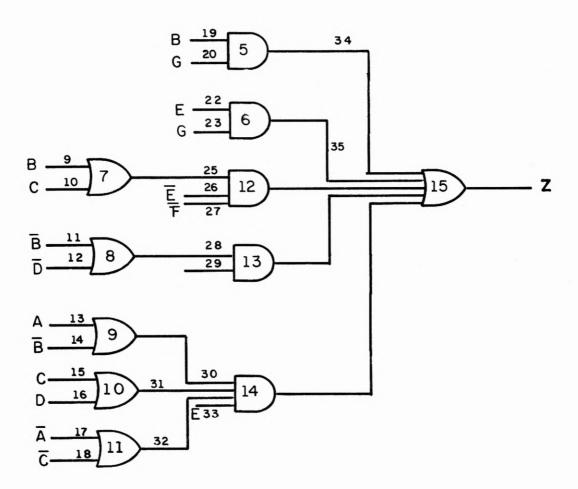

Example 3.3: In this simple example, we try to explain how the algebraic and table methods verify that a set of tests is an MFDTS. Also, we show how easy and efficient the algorithm is for a tree-type network.

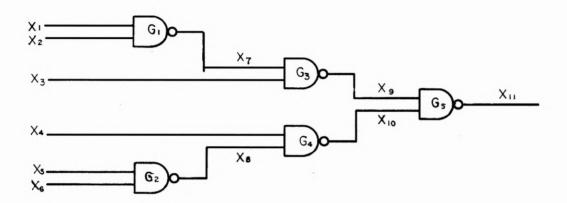

The circuit shown is Figure 3.2 has 11 lines and five gates and therefore has  $3^{11}$ -1 multiple faults or 22 single faults. To check all the multiple fault exhaustively is impractical as  $3^{11} \cong 10^5$ . By Schertz's collapsing equivalence, there are 12 single fault equivalence classes. By either the D-algorithm or any other standard method, we can generate an SFDTS for this circuit. As we examine the various SFDTS, we find that some of them are also MFDTS and some are not. Naturally, since we are interested in MFDTS, we will ask how one can determine if an SFDTS is an MFDTS. Since there are  $2^6 = 64$  different test patterns, there are 11250 different minimal SFDTS for that circuit. To find one which is an MFDTS, we can use either the algebraic method or the table method. Now, suppose we have

$$\begin{array}{l} t_1 = 011011 & : & x_1^1 \\ t_2 = 101000 & : & x_2^1 \overline{x_4^1} \\ t_3 = 110110 & : & x_6^1 \overline{x_3^1} \\ t_4 = 000101 & : & x_5^1 \overline{x_3^1} \\ t_5 = 111111 & : & x_7^1 + x_8^1 \\ t_6 = 100001 & : & x_3^1 \overline{x_2^1} + x_4^1 \overline{x_5^1} \end{array}$$

<sup>\*</sup> SFDTS = Single fault detection test set.

Figure 3.2

The set of tests  $T = \{t_1, t_2, t_3, t_4, t_5, t_6\}$  is an SFDTS. By the algebraic method, we can write

T:  $x_1^1 + x_2^1 x_4^1 + x_6^1 + x_5^1 x_3^1 + x_7^1 + x_8^1 + x_3^1 x_2^1 + x_4^1 x_5^1$  which can not be simplified to  $\sum_{i=1}^8 x_i^1$ . Therefore, T is not an MFDTS; for example, we can see T does not detect the fault  $F = \{x_2^1, x_3^1, x_4^1, x_5^1\}$ .

Now if we replace  $t_2$  by  $t_2^*$  where  $t_2^* = 101011$  :  $x_2^1$ , then  $T^* = \{t_1, t_2^*, t_3, t_4, t_5, t_6\}$  and

T:

$$x_1^1 + x_2^1 + x_6^1 + x_5^1 \overline{x_3^1} + x_7^1 + x_8^1 + x_3^1 \overline{x_2^1} + x_4^1 \overline{x_5^1}$$

=  $x_1^1 + x_2^1 + x_3^1 + x_6^1 + x_5^1 \overline{x_3^1} + x_7^1 + x_8^1 + x_4^1 \overline{x_5^1}$

=  $x_1^1 + x_2^1 + x_3^1 + x_5^1 + x_6^1 + x_7^1 + x_8^1 + x_4^1 \overline{x_5^1}$

=  $x_1^1 + x_2^1 + x_3^1 + x_4^1 + x_5^1 + x_6^1 + x_7^1 + x_8^1$

Since T' detects all the prime faults completely, T' is an MFDTS.

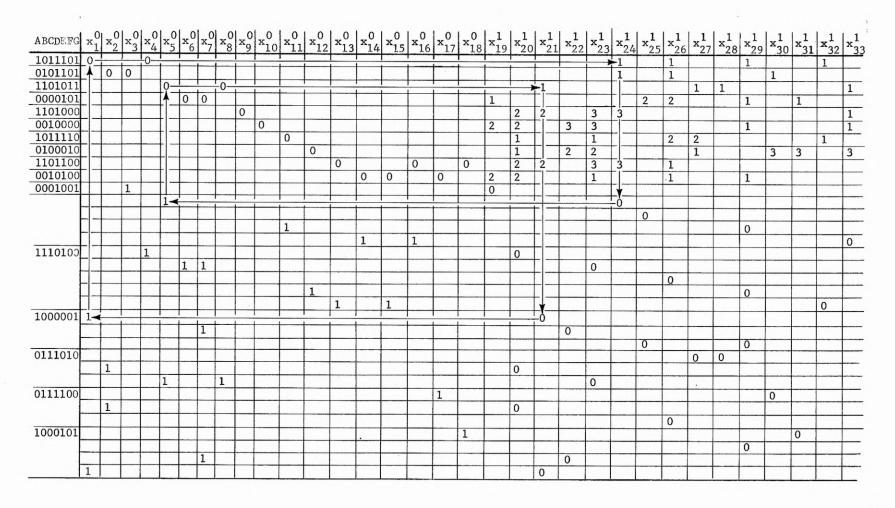

A table method is shown in Table 3.1, where Table 3.1a shows why T is not an MFDTS since there is a loop consisting of  $x_2^1, x_3^1, x_4^1, x_5^1$ . Table 3.1b shows why T' is an MFDTS since all numerals, besides 0, can be cancelled out. We explain this method in the following paragraph.

The fault table is constructed by listing every prime fault as a column heading and every generated test as the heading of at least one row. Note, one test can head more than one row if it detects more than one prime fault. For a test t which detects prime fault f with

| Prime fault | $\mathbf{x}_{1}^{1}$       | $\mathbf{x}_{2}^{1}$ | *3                                      | x <sub>4</sub> | x <sub>5</sub> <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | x <sub>6</sub>                | x <sub>7</sub> <sup>1</sup> | *8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------------------|----------------------|-----------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|