# LOW-POWER FFT VIA REDUCED PRECISION REDUNDANCY

Srinivasa Raghavan Sridhara

Coordinated Science Laboratory

1308 West Main Street, Urbana, IL 61801

University of Illinois at Urbana-Champaign

| SECURITY CLASSIFICATION OF THIS PAGE                                                                                                                                                                                                                                          |                                                                                                                      |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------|--|

| REPORT I                                                                                                                                                                                                                                                                      | DOCUMENTATIO                                                                                                         |                                                                                               | Visit of department of the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          | Form Approved<br>OMB No. 0704-0188                                                        |  |

| 1a. REPORT SECURITY CLASSIFICATION                                                                                                                                                                                                                                            |                                                                                                                      | 1b. RESTRICTIVE N                                                                             | MARKINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          |                                                                                           |  |

| Unclassified                                                                                                                                                                                                                                                                  |                                                                                                                      | None 3. DISTRIBUTION                                                                          | AVAII ABILITY A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E REPORT                                 | , —                                                                                       |  |

| 2a. SECURITY CLASSIFICATION AUTHORITY                                                                                                                                                                                                                                         |                                                                                                                      | ł                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                           |  |

| 2b. DECLASSIFICATION/DOWNGRADING SCHEDULE                                                                                                                                                                                                                                     |                                                                                                                      | Approved for public release; distribution unlimited                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                           |  |

| 4. PERFORMING ORGANIZATION REPORT NUMB                                                                                                                                                                                                                                        | ER(S)                                                                                                                | 5. MONITORING                                                                                 | ORGANIZATION F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EPORT NUM                                | MBER(S)                                                                                   |  |

| UILU-ENG-02-2220                                                                                                                                                                                                                                                              | (DAC 90)                                                                                                             |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                           |  |

| 6a. NAME OF PERFORMING ORGANIZATION                                                                                                                                                                                                                                           | 6b. OFFICE SYMBOL (If applicable)                                                                                    | 7a. NAME OF MO                                                                                | ONITORING ORGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NIZATION                                 |                                                                                           |  |

| Coordinated Science Lab<br>University of Illinois                                                                                                                                                                                                                             | N/A                                                                                                                  | NSF                                                                                           | 9.<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                          |                                                                                           |  |

|                                                                                                                                                                                                                                                                               | 1.7.2.                                                                                                               | 7h ADDRESS (Cit                                                                               | v State and ZIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Code)                                    |                                                                                           |  |

| 6c ADDRESS (City, State, and ZIP Code) 1308 W Main St Urbana, IL 61801                                                                                                                                                                                                        |                                                                                                                      | 7b. ADDRESS (City, State, and ZIP Code) 4201 Wilson Blvd Arlington, VA 22230                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                           |  |

| Ba: NAME OF FUNDING/SPONSORING<br>ORGANIZATION<br>NSF                                                                                                                                                                                                                         | 8b. OFFICE SYMBOL<br>(If applicable)                                                                                 | 9. PROCUREMEN                                                                                 | T INSTRUMENT II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DENTIFICATI                              | ON NUMBER                                                                                 |  |

| 8c. ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                                                                       |                                                                                                                      | 10. SOURCE OF F                                                                               | UNDING NUMBE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RS                                       |                                                                                           |  |

| 4201 Wilson Blvd                                                                                                                                                                                                                                                              |                                                                                                                      | PROGRAM<br>ELEMENT NO.                                                                        | PROJECT<br>NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TASK<br>NO.                              | WORK UNIT<br>ACCESSION NO.                                                                |  |

| Arlington, VA 22230                                                                                                                                                                                                                                                           |                                                                                                                      | ELEMENT NO.                                                                                   | NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ,,,,                                     |                                                                                           |  |

| Low-Power FFT Via Reduced  12. PERSONAL AUTHOR(S)  Sridhara, Srinivasa Ragha  13a. TYPE OF REPORT Technical 16. SUPPLEMENTARY NOTATION                                                                                                                                        | van                                                                                                                  | 14. DATE OF REPO                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | n, Day) 15                               | PAGE COUNT 43                                                                             |  |

| 17. COSATI CODES                                                                                                                                                                                                                                                              | 18. SUBJECT TERMS                                                                                                    | (Continue on rever                                                                            | se if necessary a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nd identify                              | by block number)                                                                          |  |

| FIELD GROUP SUB-GROUP                                                                                                                                                                                                                                                         | DSP, low-p                                                                                                           |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                           |  |

|                                                                                                                                                                                                                                                                               |                                                                                                                      |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |                                                                                           |  |

| 19. ABSTRACT (Continue on reverse if necessal Low-power design of digital sign applications. Voltage overscaling an significant power savings over and be novel ANT scheme referred to as redu We employ arithmetic unit architecture power savings can be achieved in button | nal processing (DSP)<br>d algorithmic noise<br>yond that achievable<br>ced precision redundates<br>that are the most | ) systems is crit<br>tolerance (AN<br>through voltage<br>ancy for low-pove<br>suitable for vo | T) techniques scaling alone wer fast Fourie olders over scale over | are a re. In this ter transfor ing and s | means of achieving<br>thesis, we propose a<br>m (FFT) processors.<br>how that significant |  |

| 20. DICTRIBUTION (AVAILABLETY OF ADDITION                                                                                                                                                                                                                                     |                                                                                                                      | 21 ABSTRACES                                                                                  | SECURITY CLASSII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | FICATION                                 |                                                                                           |  |

| 20. DISTRIBUTION / AVAILABILITY OF ABSTRACE   ☑ UNCLASSIFIED/UNLIMITED ☐ SAME A                                                                                                                                                                                               |                                                                                                                      | 1                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ,0,11011                                 |                                                                                           |  |

| 22a. NAME OF RESPONSIBLE INDIVIDUAL                                                                                                                                                                                                                                           |                                                                                                                      |                                                                                               | (Include Area Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ode) 22c. C                              | OFFICE SYMBOL                                                                             |  |

#### LOW-POWER FFT VIA REDUCED PRECISION REDUNDANCY

#### BY

#### SRINIVASA RAGHAVAN SRIDHARA

B. Tech., Indian Institute of Technology, Kharagpur, 1999

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2002

Urbana, Illinois

© Copyright by Srinivasa Raghavan Sridhara, 2002

## ACKNOWLEDGMENTS

I would like to thank Prof. Naresh Shanbhag for his advice and support. I would like to thank all members of the ViPS group for providing a stimulating environment for research. I am indebted to my parents and my sisters, Manjula and Sandhya, for their love and constant encouragement.

# TABLE OF CONTENTS

| CI | IAPTER                                           | PAGE |

|----|--------------------------------------------------|------|

| 1  | INTRODUCTION                                     | . 1  |

|    | 1.1 Motivation                                   |      |

|    | 1.2 Algorithmic Noise Tolerance                  |      |

|    | 1.3 Arithmetic Units                             |      |

|    | 1.4 Thesis Organization                          |      |

| 2  | LOW-POWER FFT                                    | . 6  |

|    | 2.1 Reduced Precision Redundancy                 |      |

|    | 2.1.1 VOS error characteristics                  |      |

|    | 2.1.2 Reduced precision system                   |      |

|    | 2.2 FFT Algorithm and Architecture               | _    |

|    | 2.3 Multiplier with Reduced Precision Redundancy |      |

|    | 2.3.1 The FFT multiplier                         |      |

|    | 2.3.2 Reduced precision multiplier               | . 12 |

|    | 2.3.3 Decision threshold and comparator          | . 13 |

|    | 2.4 Simulation Results                           | . 15 |

|    | 2.4.1 Performance metrics                        |      |

|    | 2.4.2 Performance of RPR                         |      |

|    | 2.5 Conclusions                                  |      |

| 3  | SOFT DSP AWARE ARITHMETIC UNITS                  | . 20 |

| Ū  | 3.1 Delay Balancing vs. VOS                      |      |

|    | 3.2 Inherent Delay Imbalance                     |      |

|    | 3.3 Adders with Voltage Overscaling              |      |

|    | 3.4 Multipliers with Voltage Overscaling         | . 29 |

|    | 3.5 Conclusions                                  | . 32 |

|    |                                                  |      |

| 4  | CONCLUSIONS AND FUTURE WORK                      | . 33 |

|    | 4.1 Summary                                      |      |

|    | 4.2 Future Work                                  | . 34 |

|    | REFERENCES                                       | . 35 |

# LIST OF TABLES

| Table |                                                                                    | Pag | е |

|-------|------------------------------------------------------------------------------------|-----|---|

| 3.1   | Power and delay for 16-bit adders from [4] relative to ripple carry adder          | . 2 | 7 |

| 3.2   | Power and delay for $16 \times 16$ multipliers relative to Baugh-Wooley multiplier | . 3 | 0 |

## LIST OF FIGURES

| Figu | re                                                                                            | Page |

|------|-----------------------------------------------------------------------------------------------|------|

| 1.1  | A soft DSP with a generic algorithmic noise tolerance (ANT) scheme                            | 3    |

| 2.1  | Overview of the proposed algorithmic noise tolerance (ANT) scheme using reduced               |      |

|      | precision redundancy                                                                          | 7    |

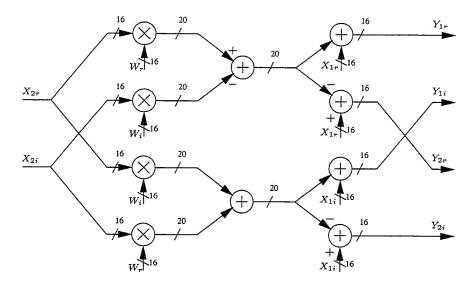

| 2.2  | Decimation-in-time butterfly                                                                  | 10   |

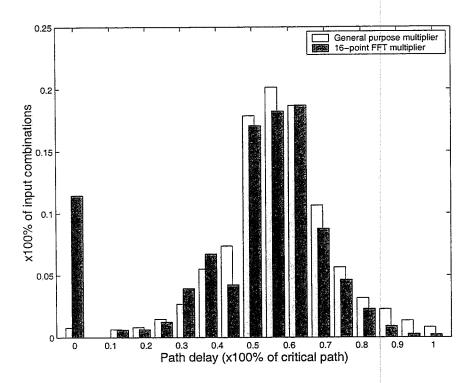

| 2.3  | Path delay distribution of an $8 \times 8$ Baugh-Wooley multiplier                            | 11   |

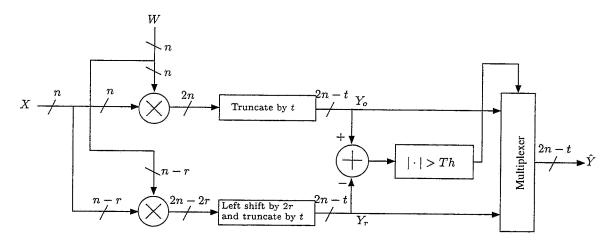

| 2.4  | Multiplier with reduced precision redundancy                                                  | 12   |

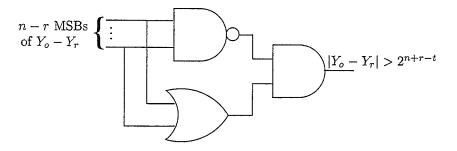

| 2.5  | Comparator $ Y_o - Y_r  > Th$ when $Th = 2^{n+r-t}$                                           | 14   |

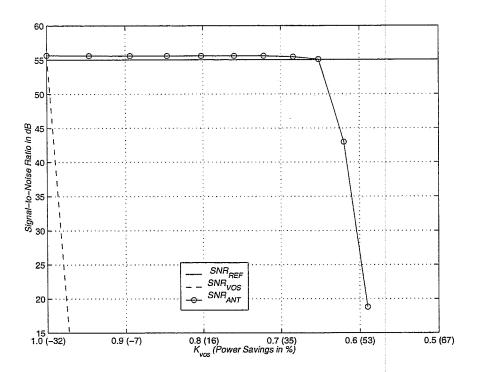

| 2.6  | $SNR$ vs. $K_{vos}$ for 0.25- $\mu$ m CMOS technology with $\alpha = 1.2$ . The corresponding |      |

|      | power savings are shown in parentheses                                                        | 17   |

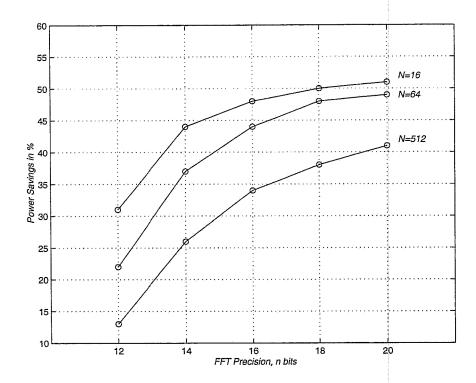

| 2.7  | Variation of power savings with FFT precision $n$ and FFT block length $N.$                   | 19   |

| 3.1  | Delay balancing to reduce glitches: (a) delay imbalanced circuit and (b) circuit              |      |

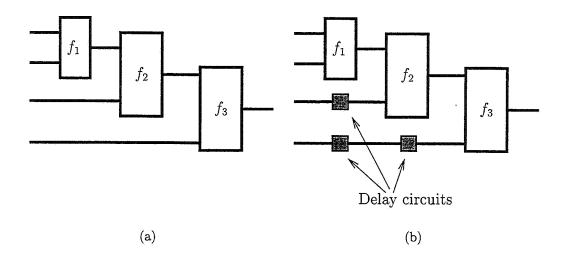

|      | with delay balancing                                                                          | 22   |

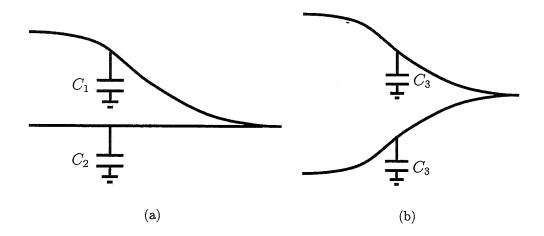

| 3.2  | (a) Circuit I with delay imbalance and (b) circuit II with inherent delay balance.            | 24   |

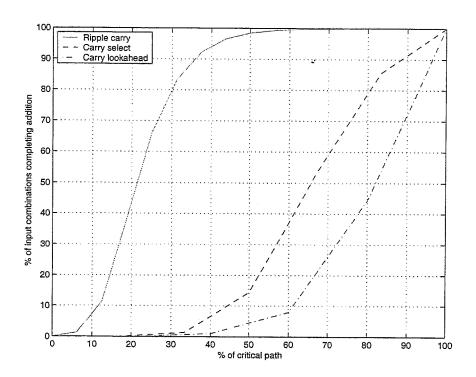

| 3.3  | Cumulative path delay distribution of 16-bit adders                                           | 28   |

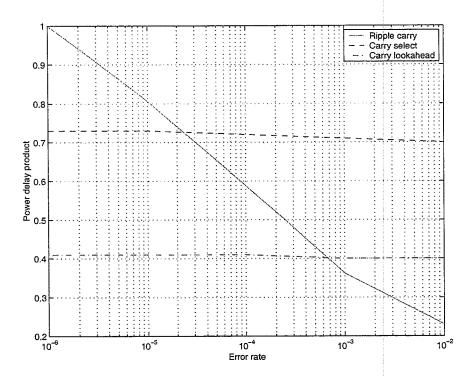

| 3.4  | Power-delay product vs. error rate                                                            | 29   |

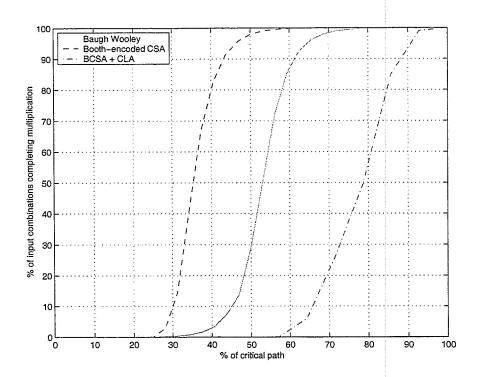

| 3.5  | Cumulative path delay distribution of 16 × 16 multipliers                                     | 31   |

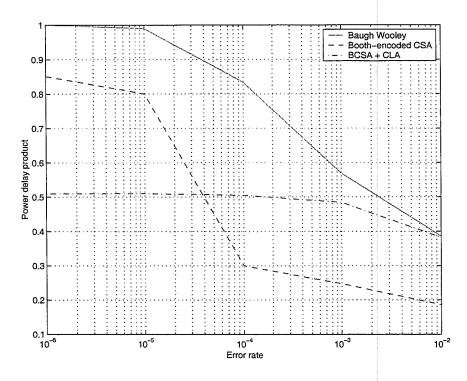

| 3.6  | Power-delay product vs. error rate                                                            | 31   |

## CHAPTER 1

## INTRODUCTION

#### 1.1 Motivation

Low-power design of digital signal processing (DSP) systems is critical in supporting next generation wireless applications. Energy efficient implementation of VLSI systems is also important to reduce packaging costs, improve reliability, and increase operational life of the circuits. The three components of power consumption in digital VLSI circuits are dynamic power dissipation, short circuit power dissipation, and leakage power dissipation. The dynamic component is the dominant source of power dissipation and depends on the circuit parameters as follows [1]:

$$P = tC_L V_{dd}^2 f_s, (1.1)$$

where t is the transition activity,  $C_L$  is effective load capacitance,  $V_{dd}$  is the operating supply voltage, and  $f_s$  is the clock frequency.

Since the dynamic power dissipation depends on the square of the supply voltage, aggressive scaling of supply voltage has been widely used to reduce the power consumption in VLSI circuits. However, scaling of the supply voltage  $V_{dd}$  increases the circuit delay  $\tau_d$  as shown below:

$$\tau_d = \frac{C_L V_{dd}}{\beta (V_{dd} - V_t)^{\alpha}},\tag{1.2}$$

where  $\alpha$  is the velocity saturation index,  $\beta$  is the gate transconductance, and  $V_t$  is the device threshold voltage. The increased circuit delay results in loss of system throughput. Hence, power reduction in conventional voltage-scaled systems is limited by a minimum supply voltage  $V_{dd-crit}$  at which the throughput requirements of the system are just met.

## 1.2 Algorithmic Noise Tolerance

Recently, voltage overscaling (VOS) [2] in combination with algorithmic noise-tolerance (ANT) has been proposed as a means of achieving significant power savings over and beyond that achievable by voltage scaling alone. VOS refers to the scaling of supply voltage beyond  $V_{dd-crit}$ , without sacrificing the throughput, i.e.,

$$V_{dd} = K_{vos} V_{dd-crit}, \ 0 \le K_{vos} < 1,$$

(1.3)

where  $K_{vos}$  is the VOS factor. VOS makes the critical path delay  $T_{cp} > T_s$ , where  $T_s$  is the clock period. This results in input-dependent (hence intermittent or soft) errors whenever paths with delays greater than  $T_s$  are excited, leading to a severe signal-to-noise ratio (SNR) loss.

Energy-efficient means of compensating for these soft errors is achieved via ANT [2], [3]. The ANT technique uses an error control block that mitigates the effect of soft errors

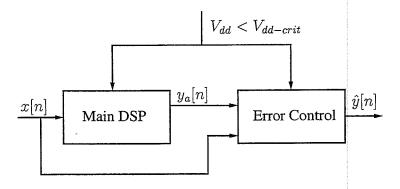

Figure 1.1 A soft DSP with a generic algorithmic noise tolerance (ANT) scheme.

occurring at the output of a DSP block with VOS. Figure 1.1 shows a *soft DSP* system using a generic ANT scheme. In prediction based ANT schemes [2], a linear predictor is used as the error control block to restore the *SNR* in a narrowband frequency-selective filter. The adaptive error-cancellation [3] based ANT scheme models the error using an adaptive filter and cancels the estimated error from the output of main DSP.

The prediction and adaptive error cancellation based techniques are suitable for frequency-selective filtering. In this thesis, we employ a novel ANT scheme referred to as reduced precision redundancy (RPR) to significantly reduce the power dissipation in the butterfly functional unit of a fast Fourier transform (FFT) processor.

As supply voltage  $V_{dd}$  approaches the threshold voltage  $V_t$  in future technologies, voltage scaling and, in particular, VOS, may not remain a viable means of power reduction due to the resulting severe delay penalty. However, the soft errors also occur if the clock frequency is increased beyond a critical frequency  $f_{crit}$  (frequency overscaling). Therefore, ANT schemes can be used in the design of high-speed DSP systems with marginal penalty in power. Further, ANT schemes can be used to mitigate the effects of deep submicron noise and process variations [2] resulting in robust DSP systems.

#### 1.3 Arithmetic Units

Power consumption in a given DSP datapath is determined by the power dissipated in the arithmetic units present in the datapath. Therefore, minimizing the power consumption of arithmetic units is of great importance. Since performance is often limited by arithmetic units' speed, it is also important to maximize speed. Frequently, the compromise between these conflicting demands of low power dissipation and high speed can be accomplished by selecting the arithmetic unit that has the minimum power-delay product.

Extensive studies have been done to compare a variety of adders [4] and multipliers [5] based on their power-delay product. However, it was shown in [2] that the frequency of soft errors due to voltage overscaling mainly depends on the path delay distribution of the arithmetic units. Specifically, it was shown that delay imbalance in arithmetic units increases the achievable power savings. Therefore, to select a suitable arithmetic unit for a soft DSP system, we not only need to consider the power-delay product but also study the delay imbalance of the arithmetic unit. In this thesis, we study the delay imbalance of various adders and multipliers and determine the soft DSP friendly architectures.

## 1.4 Thesis Organization

The rest of this thesis is organized as follows. In Chapter 2, we introduce the novel reduced precision redundancy (RPR) technique for mitigating the degradation in SNR due to VOS. An FFT multiplier architecture that employs the proposed RPR scheme

is presented. Extensive simulation results show the achievable power savings using the proposed scheme.

In Chapter 3, we show how delay imbalance helps voltage overscaling. We study the delay imbalance present in a variety of adders and multipliers and show that the arithmetic units with higher delay imbalance perform better with VOS. We use the result of the comparison to further improve the power savings achieved in the FFT architecture with the RPR scheme.

In Chapter 4, we present the conclusions and outline possible future work.

#### CHAPTER 2

#### LOW-POWER FFT

A low-power implementation of the fast Fourier transform (FFT) is critical in supporting next generation wireless LAN and wireless access systems. These systems are based upon orthogonal frequency division multiplexing (OFDM) [6], [7] requiring FFT processors in the transceivers. In the past, aggressive scaling of the supply voltage has been employed to reduce the power consumption in FFT processors [7], [8] so as to meet the stringent power budget of such systems. However, as described in Chapter 1, scaling of the supply voltage  $V_{dd}$  increases the circuit delay  $\tau_d$ , resulting in processor throughput loss. Hence, we apply VOS to achieve power savings over and beyond that achievable by voltage scaling alone.

In this chapter, we introduce a novel ANT scheme referred to as reduced precision redundancy (RPR) [9], [10] to restore the performance degradation at the output of the FFT processor due to VOS. We present the proposed technique in Section 2.1. We describe the architecture of a typical FFT processor in Section 2.2 and identify multipliers as the major sources of power consumption in an FFT butterfly. In Section 2.3, we describe how RPR can be applied to FFT multipliers. Simulation results are presented in Section 2.4 and conclusions are in Section 2.5.

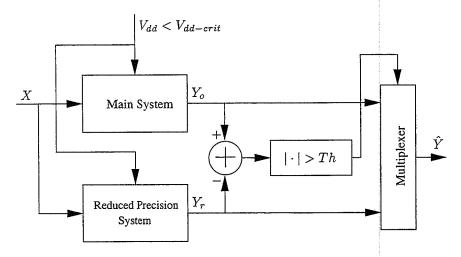

Figure 2.1 Overview of the proposed algorithmic noise tolerance (ANT) scheme using reduced precision redundancy.

## 2.1 Reduced Precision Redundancy

In this section, we describe the reduced precision redundancy (RPR) based ANT scheme. The proposed soft DSP system is shown in Figure 2.1, where a reduced precision replica operates in parallel with the main system with VOS in order to detect and correct errors. We first describe the error characteristics of the output of the main system due to VOS and then present the proposed scheme.

#### 2.1.1 VOS error characteristics

Voltage overscaling introduces input-dependent soft errors whenever a path with delay greater than the clock period  $T_s$  is excited. Since most of the arithmetic units employed in DSP systems are based on least significant bit (LSB) first computation, soft errors appear first in the most significant bits (MSBs), resulting in errors of large magnitude.

These errors, though they degrade the performance severely, are desirable as they are easier to detect if the correct MSB information is known.

#### 2.1.2 Reduced precision system