University of Illinois at Urbana-Champaign

Accurate Power Estimation for Large Sequential Circuits

Joseph Nicolas Kozhaya

Coordinated Science Laboratory 1308 West Main Street, Urbana, IL 61801

|  | OF THIS |  |

|--|---------|--|

|  |         |  |

|  |         |  |

|  |         |  |

|  |         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REPORT DOCUMENTATION       |          |                                    |                                   | N PAGE                                                          |                              |                      | Form Approved<br>OMB No. 0704-0188   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------|------------------------------------|-----------------------------------|-----------------------------------------------------------------|------------------------------|----------------------|--------------------------------------|--|

| REPORT SE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CURITY CLASSI              | FICATIO  | N                                  |                                   | 1b. RESTRICTIVE                                                 | MARKINGS                     | المتحد المحدد المتحد |                                      |  |

| Unclass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |          |                                    |                                   | None                                                            | TAVABARIETY OF               | COORT                |                                      |  |

| SECURITY C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CLASSIFICATION             | I AUTH   | OKITY                              |                                   |                                                                 | /AVAILABILITY OF I           | •                    | '                                    |  |

| DECLASSIFI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CATION/DOW                 | NGRAD    | ING SCHEDUL                        | E                                 | ~ ~                                                             | or public religion unlimited | rease                | 3                                    |  |

| ERFORMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | G ORGANIZATI               | ON REF   | ORT NUMBER                         | R(S)                              | 5. MONITORING                                                   | ORGANIZATION REP             | ORT NU               | MBER(S)                              |  |

| UILU-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ENG-98-22                  | 15       | DAC-65                             |                                   |                                                                 |                              |                      |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PERFORMING C<br>ated Scien |          |                                    | 6b. OFFICE SYMBOL (If applicable) | 7a. NAME OF MO<br>SRC                                           | ONITORING ORGANI             | ZATION               |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ity of II                  |          |                                    | N/A                               | DICO                                                            |                              |                      |                                      |  |

| ADDRESS (City, State, and ZIP Code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |          |                                    |                                   |                                                                 | y, State, and ZIP Co         | de)                  |                                      |  |

| 1308 W Main St<br>Urbana, IL 61801                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                            |          |                                    | PO 12053                          | Iriangle Park                                                   | NC                           | 27709                |                                      |  |

| urbana,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Tr 0100                    | ı        |                                    |                                   | Research .                                                      | illangie raik                | , NO                 | 2//09                                |  |

| NAME OF FUNDING/SPONSORING 8b. OFFICE SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |          |                                    | 9. PROCUREMENT                    | T INSTRUMENT IDEN                                               | ITIFICAT                     | ION NUMBER           |                                      |  |

| ORGANIZATION (If applicable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |          | (If applicable)                    |                                   |                                                                 |                              |                      |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |          |                                    |                                   | 96-DP-109                                                       |                              |                      |                                      |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | lity, State, and           | ZIP COC  | ie)                                |                                   | 10. SOURCE OF F                                                 | PROJECT                      | TASK                 | WORK UNIT                            |  |

| 0 12053                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |          |                                    | ELEMENT NO.                       |                                                                 | NO.                          | ACCESSION NO.        |                                      |  |

| .esearch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Triangle                   | Park     | , NC 277                           | 709                               |                                                                 |                              |                      |                                      |  |

| TITLE (Inclu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ide Security Cl            | assifica | tion)                              |                                   |                                                                 |                              |                      |                                      |  |

| ccurate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power Est                  | imat     | ion for I                          | arge Sequential                   | Circuits                                                        |                              |                      |                                      |  |

| PERSONAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AUTHOR(S)                  |          | <del> </del>                       |                                   |                                                                 | <u> </u>                     |                      |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Joseph Ni                  | cola     | مناسب فيصار المساقي الأراث والمساق |                                   |                                                                 |                              | <del></del>          | 2.65 621117                          |  |

| n TYPE OF<br>Technic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |          | FROM                               | OVERED                            | 14. DATE OF REPO                                                | RT (Year, Month, D.<br>25    | ay) 15               | . PAGE COUNT<br>39                   |  |

| SUPPLEME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NTARY NOTAT                | ION      |                                    | •                                 |                                                                 |                              |                      |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |          |                                    |                                   |                                                                 |                              | one see              |                                      |  |

| FIELD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | COSATI (                   |          | 3-GROUP                            | 1                                 | (Continue on reverse if necessary and identify by block number) |                              |                      |                                      |  |

| 1,000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JACOF                      | 300      |                                    | •                                 | ion; sequential circuit; random sampling;                       |                              |                      |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |          |                                    | power vector s                    |                                                                 |                              |                      |                                      |  |

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (Continue on               | reverse  | if necessary                       | and identify by block n           | umber)                                                          |                              |                      |                                      |  |

| The average power dissipation of a logic circuit depends on the input vector set. For sequential circuits, performing power estimation based on randomly generated vectors (based on some assumed or measured signal activity and probability values) can lead to power estimates that are completely wrong. This is because the real vector set (as opposed to a randomly generated vector set) may contain specific vector sequences that put the circuit in specific operational modes or subspaces of its large state space and, in different operational modes, the circuit may dissipate quite different values of power. Essentially, simulation with unrealistic vectors can take the circuit to parts of the state space where it was never meant to operate, and once this happens, the estimated power dissipation can be completely different from what the circuit would dissipate under realistic legal operation. This is a common problem in most existing power estimation methods. However, simulating real vector sets for purposes of power estimation can be very expensive because the vector set (in order to be representative of the real power) can be huge. To solve this problem, a power estimation approach is presented in which blocks of consecutive vectors are selected at random from a user-supplied realistic input vector set and the circuit is simulated for each block starting from an unknown state. This leads to two (upper and lower) bounds on the desired power value which can be quite tight (under 10% difference between the two in many cases). As a result, the power dissipation is obtained by simulating only a fraction of the potentially very large vector set.  DISTRIBUTION/AVAILABILITY OF ABSTRACT    21. ABSTRACT SECURITY CLASSIFICATION   Unclassified |                            |          |                                    |                                   |                                                                 |                              |                      |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            | -        | <u>-</u>                           | RPT. DTIC USERS                   | Unclassif                                                       |                              | ION                  |                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RESPONSIBLE                |          |                                    |                                   |                                                                 | (Include Area Code)          | 22c. O               | FFICE SYMBOL                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |          | and the section of the section of  |                                   | <u> </u>                                                        |                              |                      | بالواجات والمرب يشمه الموضوع والمراب |  |

#### ACCURATE POWER ESTIMATION FOR LARGE SEQUENTIAL CIRCUITS

#### BY

#### JOSEPH NICOLAS KOZHAYA

B.E., American University of Beirut, 1996

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 1998

Urbana, Illinois

# **ABSTRACT**

The average power dissipation of a logic circuit depends on the input vector set. For sequential circuits, performing power estimation based on randomly generated vectors (based on some assumed or measured signal activity and probability values) can lead to power estimates that are completely wrong. This is because the real vector set (as opposed to a randomly generated vector set) may contain specific vector sequences that put the circuit in specific operational modes or subspaces of its large state space and, in different operational modes, the circuit may dissipate quite different values of power. Essentially, simulation with unrealistic vectors can take the circuit to parts of the state space where it was never meant to operate, and once this happens, the estimated power dissipation can be completely different from what the circuit would dissipate under realistic legal operation. This is a common problem in most existing power estimation methods. However, simulating real vector sets for purposes of power estimation can be very expensive because the vector set (in order to be representative of the real power) can be huge. To solve this problem, a power estimation approach is presented in which blocks of consecutive vectors are selected at random from a user-supplied realistic input vector set and the circuit is simulated for each block starting from an unknown state. This leads to two (upper and lower) bounds on the desired power value which can be quite tight (under 10% difference between the two in many cases). As a result, the power dissipation is obtained by simulating only a fraction of the potentially very large vector set:

# ACKNOWLEDGMENTS

I thank my academic advisor, Dr. Farid Najm, for the guidance he gave me and the time he devoted to this work. Finally, I thank my parents for their love and support throughout my life.

# TABLE OF CONTENTS

| C. | HAPTER                                                | <b>AGE</b>           |

|----|-------------------------------------------------------|----------------------|

| 1  | INTRODUCTION                                          | 1<br>2<br>3<br>5     |

| 2  | PROPOSED APPROACH                                     | 6<br>6<br>9          |

| 3  | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 12<br>12<br>14<br>18 |

| 4  | RESULTS                                               | 22                   |

| 5  | CONCLUSIONS                                           | 28                   |

|    | REFERENCES                                            | 29                   |

# LIST OF TABLES

| Tab | ple F                                                                                                                                                                  | age |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Differences in power values (in mW) due to the presence of correlation in the vector set                                                                               | 8   |

| 4.1 | Performance under correlated input vectors while using the fixed block size approach. Execution time was measured on a SUN Sparc 5                                     | 23  |

| 4.2 | Performance under correlated input vectors while using the variable block size approach with a tightness threshold of 5%. Execution time was measured on a SUN Sparc 5 | 24  |

| 4.3 | Error between simulation of all 100,000 correlated vectors and using the Block                                                                                         | 27  |

|     | Sampling (BS) scheme (applied with variable block size)                                                                                                                | 25  |

| 4.4 | Results obtained by using the exact approach as well as the error resulting from using the approximation. Power values (LB, UB, and Power) are all                     |     |

|     | given in mW                                                                                                                                                            | 27  |

|     |                                                                                                                                                                        |     |

# LIST OF FIGURES

| Figu | ıre F                                                                                                         | age |

|------|---------------------------------------------------------------------------------------------------------------|-----|

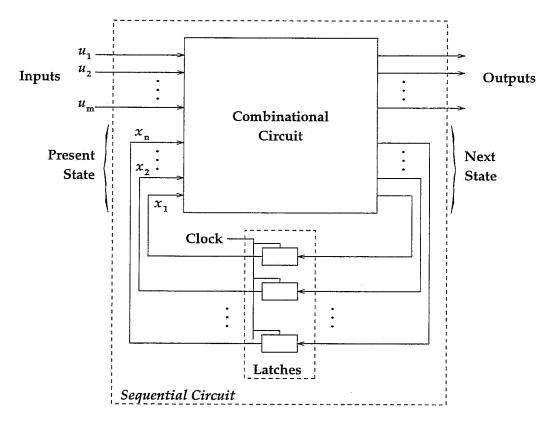

| 2.1  | An FSM model of a sequential logic circuit.                                                                   | 10  |

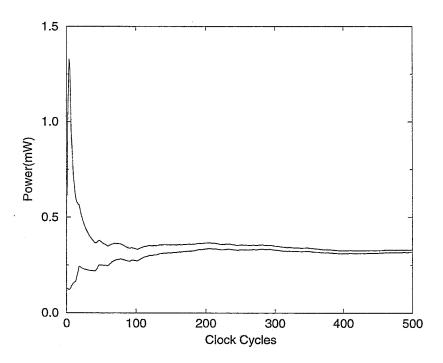

| 3.1  | Upper and lower power bounds under a correlated vector set for circuit s1423 (74 latches and 657 gates)       | 15  |

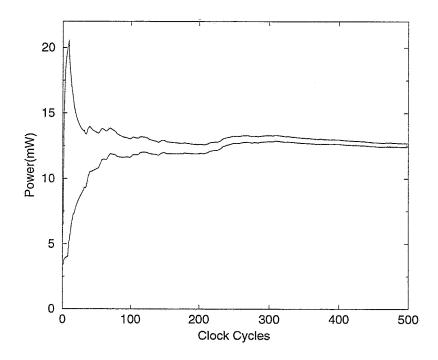

| 3.2  | Upper and lower power bounds under a correlated vector set for circuit s35932 (1728 latches and 16,065 gates) | 16  |

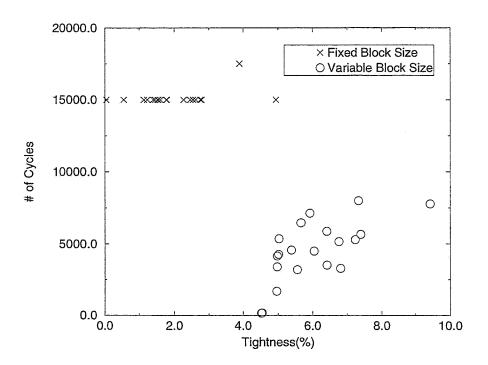

| 3.3  | Comparison between the fixed and variable block size approaches                                               |     |

# CHAPTER 1

# INTRODUCTION

Maximizing circuit speed and minimizing chip area used to be the only major concerns of VLSI designers. In recent years, power consumption of integrated circuits (ICs) has proved to be just as important of a concern. Thus, VLSI designs nowadays emerge as a trade-off between three goals: minimum area, maximum speed, and minimum power dissipation.

The decrease in feature size and the corresponding increase in chip density have made power dissipation a major factor in the reliability of the chip. Excessive power dissipation causes overheating and raises the device operating temperature. This may lead to soft errors as well as permanent damage. Thus elaborate and costly packaging as well as system level cooling are required. In other words, high power consumption results in higher risk and consequently higher cost.

In addition to the reliability issue, low power designs play an important role in promoting portable applications such as cellular phones, pagers, personal digital assistants (PDAs), and laptop computers. The success of portable applications depends greatly on the availability of these applications anywhere anytime. The longer an application is available, the more desirable it is. However, the operating time of an application is limited by the battery life, i.e., the time for which the equipment can be used before having to replace or recharge the battery. To extend the operating time of a portable application, either the battery used should have a longer life or the chip used should consume less power. Because not much improvement has been cited in battery design, low power chips tend to be the better alternative.

It is clear from the above discussion that low power designs are essential to cope with the technological progress. The first step in designing for power optimization is power estimation, which is the subject of this thesis. Because most useful circuits are sequential, our work targets the average power estimation problem for large sequential circuits.

#### 1.1 Sources of Power Dissipation in CMOS Circuits

In estimating the average power dissipation of a CMOS VLSI chip, it suffices to estimate the average supply current since the supply voltage is approximately constant. Four components of the supply current can be identified [1]:

Capacitive current: This is the current responsible for charging/discharging the node capacitances during a logic transition. This current is the dominant source of power dissipation in CMOS circuits. The power dissipated because of this current is given by:

$$P = \frac{1}{2}C_L V_{dd}^2 D$$

where  $C_L$  is the physical load capacitance,  $V_{dd}$  is the supply voltage, and D is the transition density, that is, the average number of logic transitions per second.

- Short circuit current: In a CMOS circuit, during a logic transition, both the nMOS and the pMOS transistors conduct simultaneously for a short while. During that time, a short circuit is established between the power bus and ground. The current that flows in this short circuit is referred to as the short circuit current.

- Standby current: This current is continuously drawn from the power supply even in steady state. This kind of current is significant in design styles like pseudo-nMOS. Actually, such a current doesn't exist in fully complementary CMOS designs.

- Leakage current: This current further subdivides into two categories: diode leakage

and subthreshold leakage. In CMOS circuits, all source and drain diffusions constitute reverse-biased diodes in which a diode leakage current flows. However, this

current is typically small and often neglected. The subthreshold leakage current, on the other hand, is more prominent. It is due to the inversion charge that exists when the MOS transistor is supposed to be off.

#### 1.2 Previous Power Estimation Techniques

Before presenting previous work done on power estimation, we should note that by power estimation we refer to the problem of *average* power estimation. This is different from the estimation of the worst case instantaneous power. Chip reliability and equipment lifetime are directly related to the average power.