© 2022 Qingyi Wang

STABILITY ANALYSIS OF VOLTAGE-IN-CURRENT LATENCY

INSERTION METHOD

BY

QINGYI WANG

THESIS

Submitted in partial fulfillment of the requirements

for the degree of Master of Science in Electrical and Computer Engineering

in the Graduate College of the

University of Illinois Urbana-Champaign, 2022

Urbana, Illinois

Adviser:

Professor José E. Schutt-Ainé

## ABSTRACT

As the semiconductor industry produces more transistors with higher frequencies and a more compact chip design, the demand for a novel simulation tool capable of simulating large-scale circuits both quickly and accurately has been increasing. The latency insertion method (LIM) has been proposed as a viable alternative to the conventional SPICE simulator for the simulation of large networks as it enables linear numerical complexity and achieves significant speed improvement.

In this thesis, an improved version of the LIM called the voltage-in-current latency insertion method (VinC LIM) is discussed. Special attention is devoted to the stability analysis of VinC LIM. We prove and demonstrate that VinC LIM overcomes the time step size limitation that the basic LIM faces and improves the stability significantly. With the larger time steps, VinC LIM can allow the simulation to finish in a much shorter time without suffering from the stability limitation.

*To my parents, for their love and support.*

## ACKNOWLEDGMENTS

First and foremost, I would like to express my sincere gratitude to my advisor, Professor José E. Schutt-Ainé, for his continued support and guidance. Without this, I would have not been able to complete this thesis and have a fruitful graduate life.

Next, I would like to thank my parents for their unconditional love, understanding, and encouragement every step of the way. They always stand by my side and support my decisions. Without them, I would not be able to pursue my dream, with no boundaries.

In addition, I am grateful for my friends at the Electromagnetics Lab for their help and support throughout my graduate study research. Their constructive research discussions and feedbacks were critical to the completion of this thesis.

# TABLE OF CONTENTS

|                                                                    |     |

|--------------------------------------------------------------------|-----|

| LIST OF FIGURES . . . . .                                          | vi  |

| LIST OF ABBREVIATIONS . . . . .                                    | vii |

| CHAPTER 1 INTRODUCTION . . . . .                                   | 1   |

| 1.1 Motivation . . . . .                                           | 1   |

| 1.2 Background . . . . .                                           | 1   |

| 1.3 Outline . . . . .                                              | 2   |

| CHAPTER 2 LATENCY INSERTION METHOD . . . . .                       | 4   |

| 2.1 Basic Formulation . . . . .                                    | 4   |

| 2.2 Stability of LIM . . . . .                                     | 7   |

| 2.3 Summary . . . . .                                              | 10  |

| CHAPTER 3 VOLTAGE-IN-CURRENT LATENCY INSERTION<br>METHOD . . . . . | 11  |

| 3.1 Formulation . . . . .                                          | 11  |

| 3.2 Stability of VinC LIM . . . . .                                | 12  |

| 3.3 Summary . . . . .                                              | 18  |

| CHAPTER 4 APPLICATIONS . . . . .                                   | 19  |

| 4.1 Model of the Power Plane . . . . .                             | 19  |

| 4.2 Simulation Results . . . . .                                   | 20  |

| CHAPTER 5 CONCLUSION AND FUTURE WORK . . . . .                     | 28  |

| 5.1 Conclusion . . . . .                                           | 28  |

| 5.2 Future Work . . . . .                                          | 29  |

| REFERENCES . . . . .                                               | 30  |

## LIST OF FIGURES

|      |                                                                                                 |    |

|------|-------------------------------------------------------------------------------------------------|----|

| 2.1  | RLGC grid. . . . .                                                                              | 5  |

| 2.2  | LIM branch topology. . . . .                                                                    | 5  |

| 2.3  | LIM node topology. . . . .                                                                      | 6  |

| 3.1  | Single-cell circuit. . . . .                                                                    | 13 |

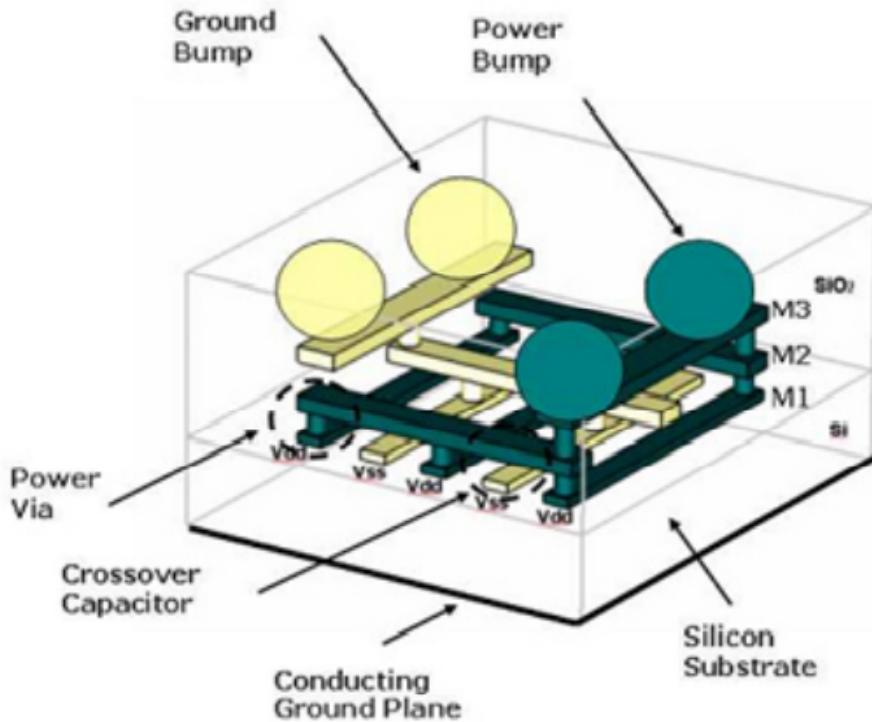

| 4.1  | Diagram of the on-chip power distribution network. . . . .                                      | 21 |

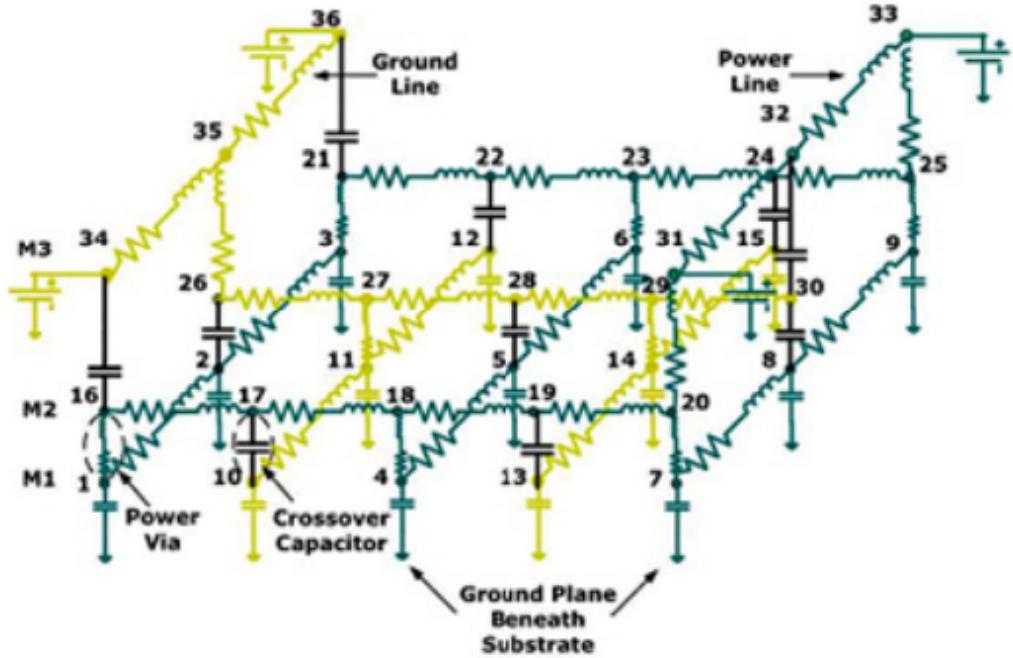

| 4.2  | Circuit model of the on-chip power distribution network. . . .                                  | 22 |

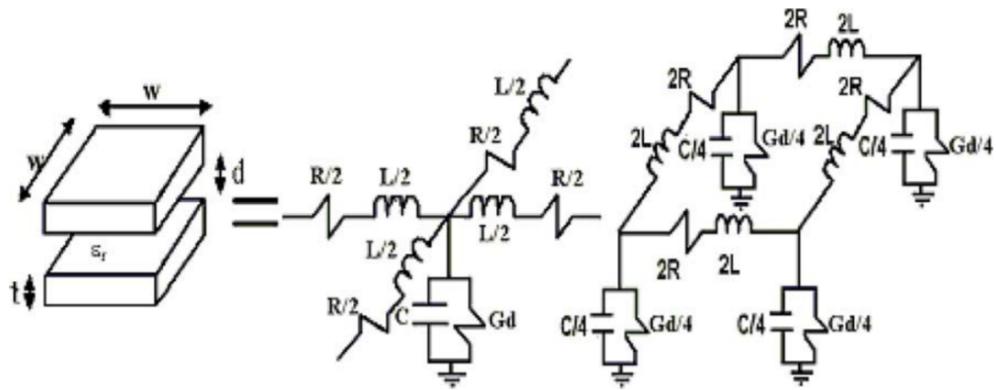

| 4.3  | Plane pair structure and the equivalent circuit of the unit cell.                               | 23 |

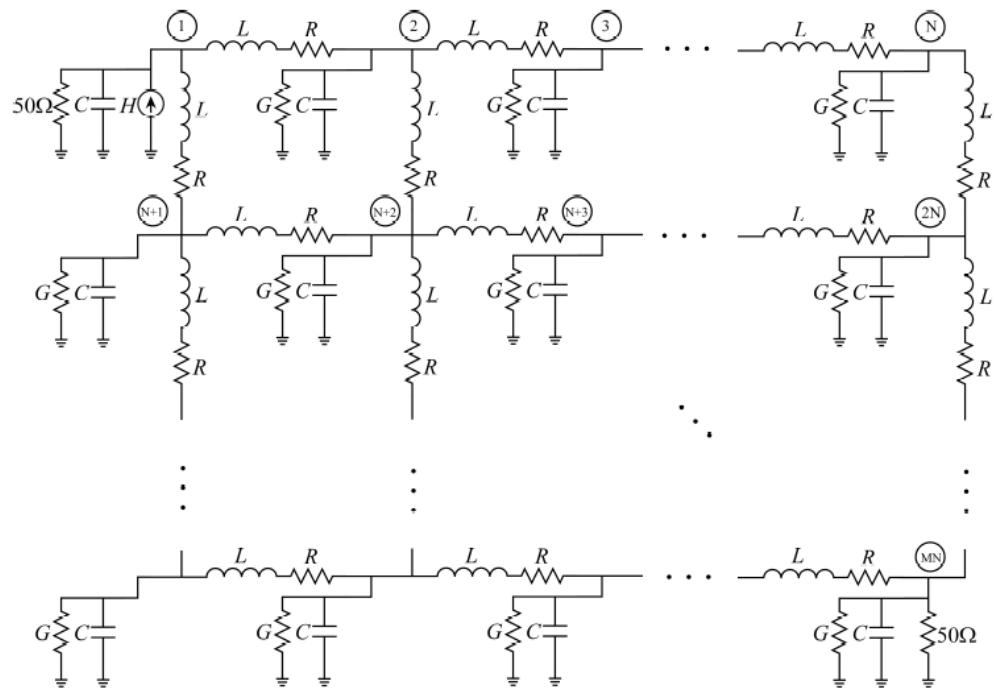

| 4.4  | Equivalent circuit model for LIM simulation. . . . .                                            | 23 |

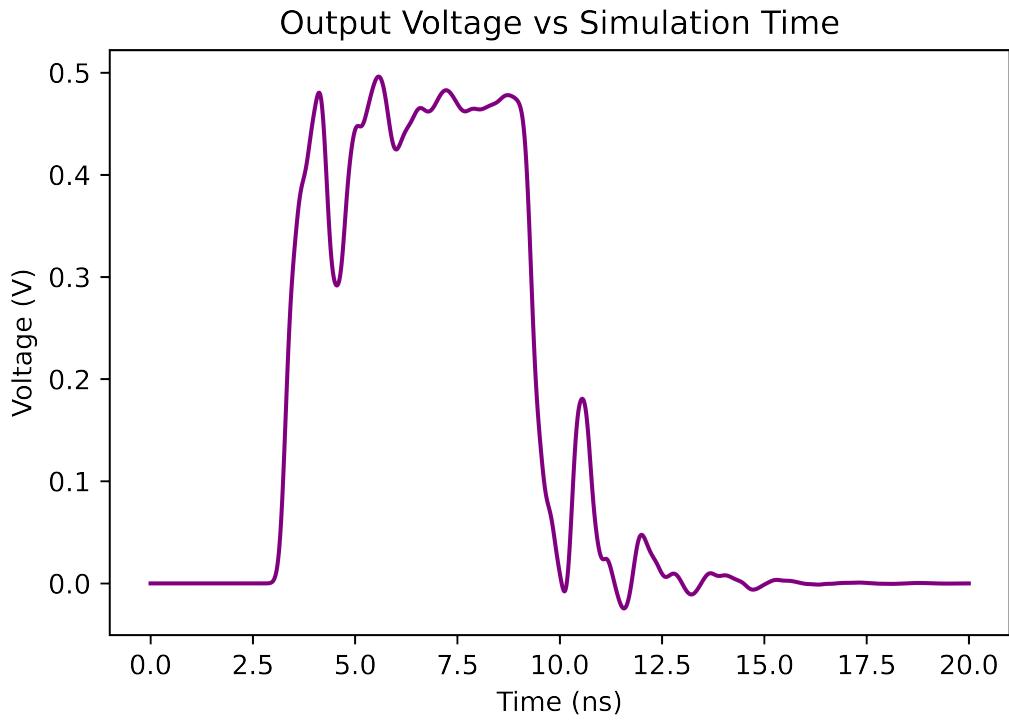

| 4.5  | Output voltage waveform from basic LIM simulation with<br>$\Delta t = 5.8 \text{ ns}$ . . . . . | 24 |

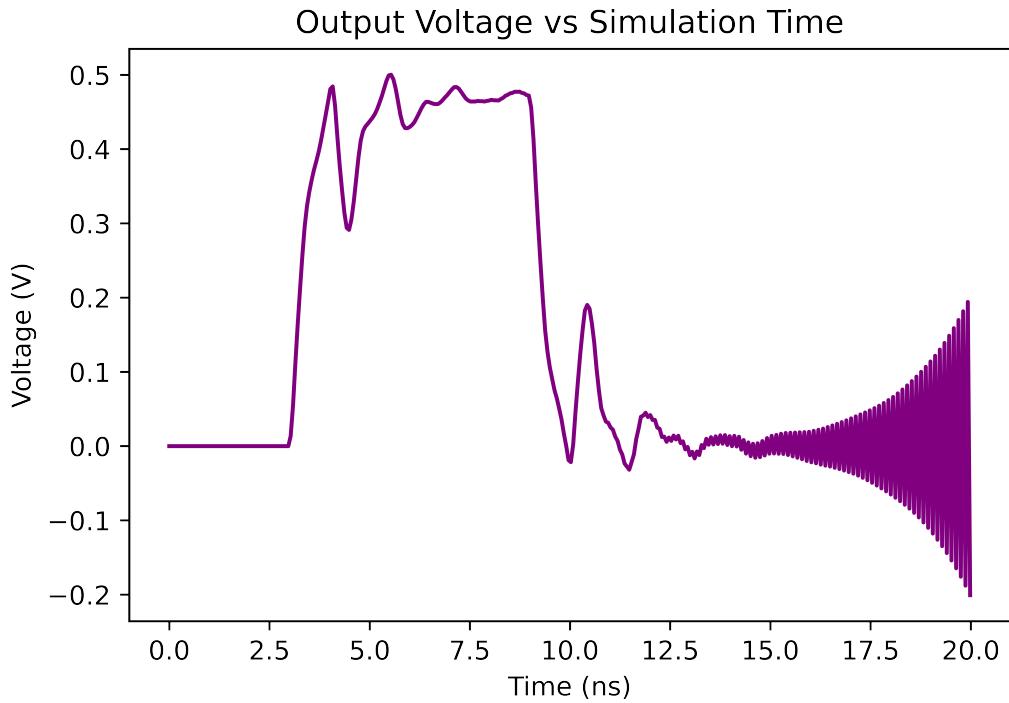

| 4.6  | Output voltage waveform from basic LIM simulation with<br>$\Delta t = 58 \text{ ns}$ . . . . .  | 24 |

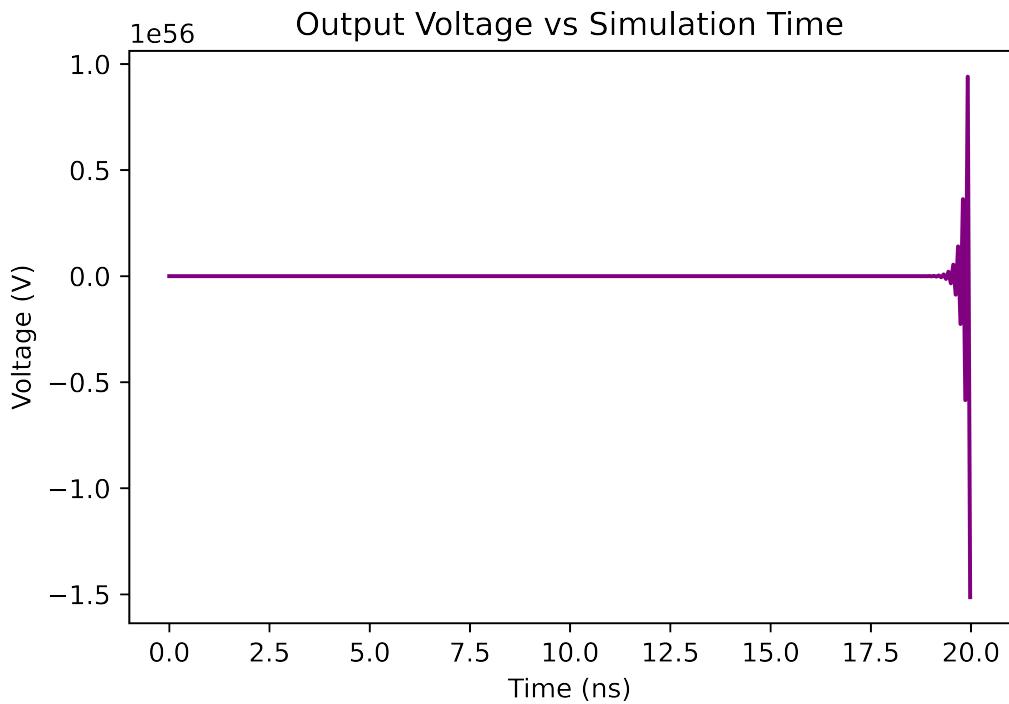

| 4.7  | Output voltage waveform from basic LIM simulation with<br>$\Delta t = 60 \text{ ns}$ . . . . .  | 25 |

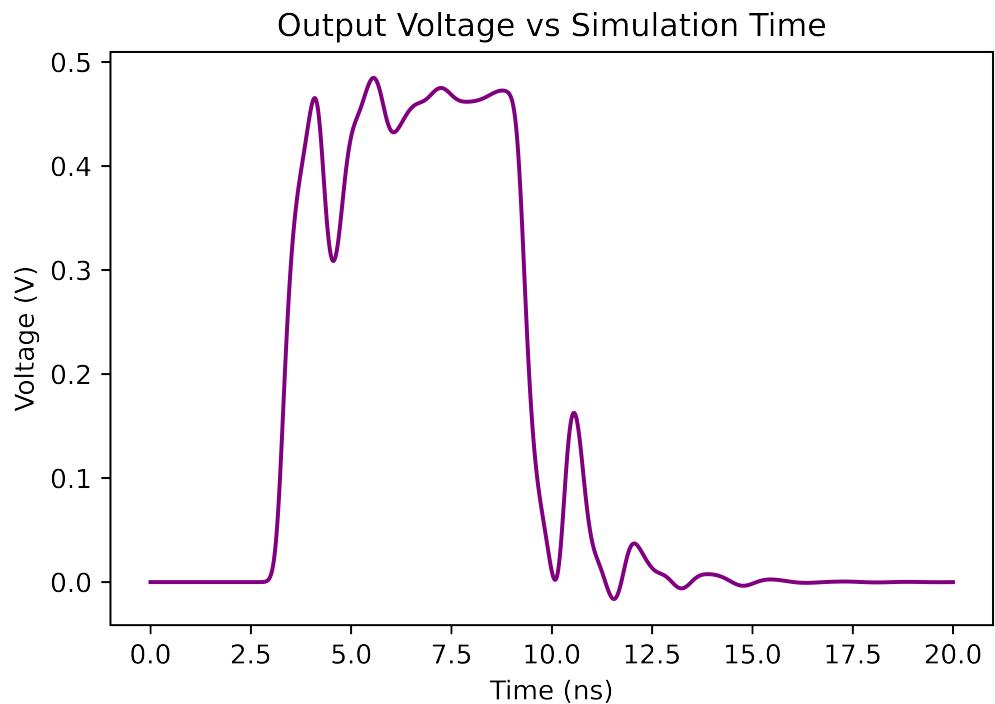

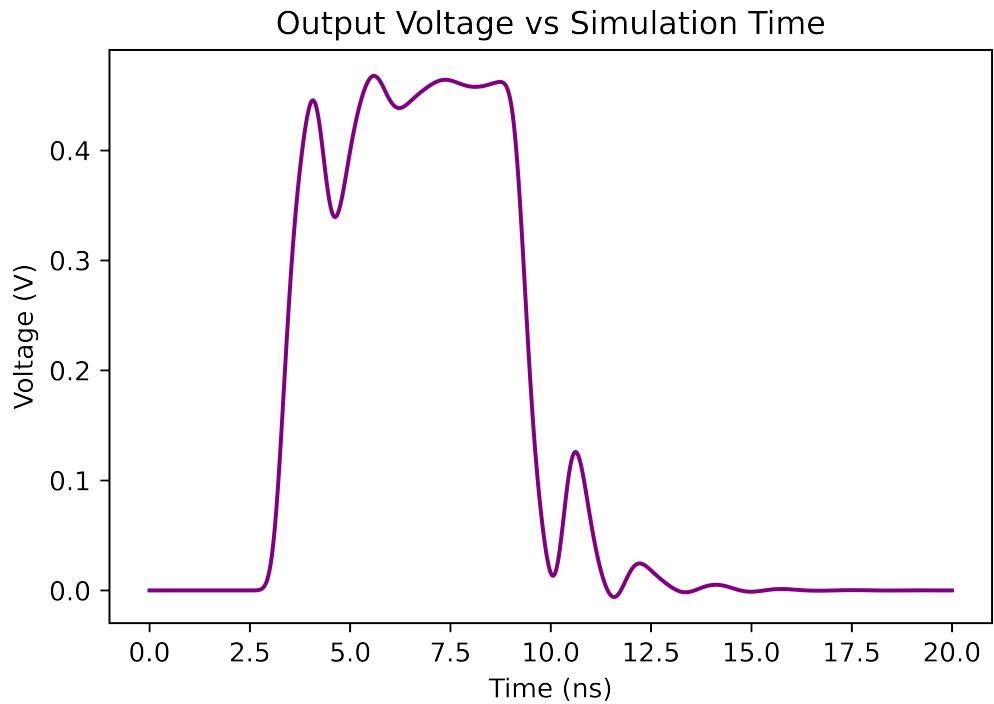

| 4.8  | Output voltage waveform from VinC LIM simulation with<br>$\Delta t = 5.8 \text{ ns}$ . . . . .  | 25 |

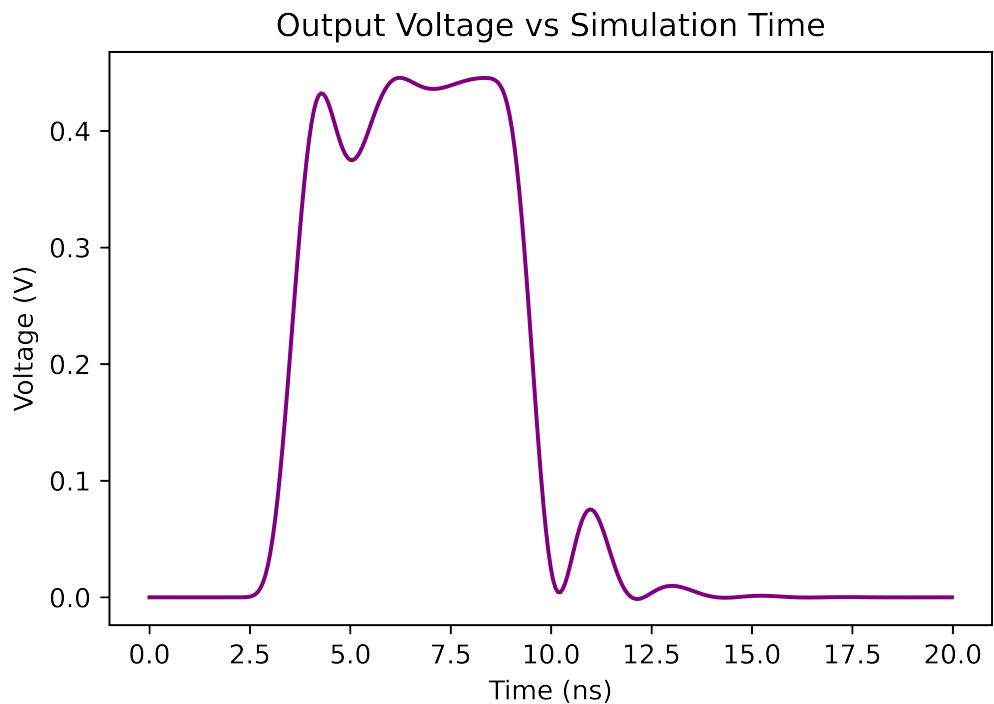

| 4.9  | Output voltage waveform from VinC LIM simulation with<br>$\Delta t = 58 \text{ ns}$ . . . . .   | 26 |

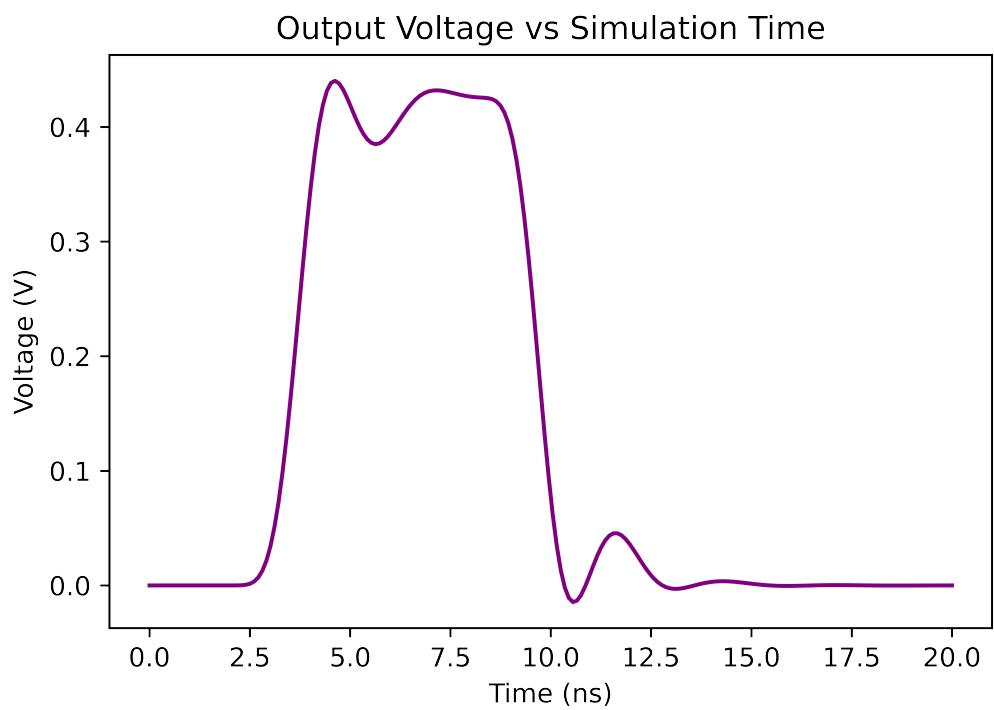

| 4.10 | Output voltage waveform from VinC LIM simulation with<br>$\Delta t = 60 \text{ ns}$ . . . . .   | 26 |

| 4.11 | Output voltage waveform from VinC LIM simulation with<br>$\Delta t = 100 \text{ ns}$ . . . . .  | 27 |

## LIST OF ABBREVIATIONS

|          |                                                         |

|----------|---------------------------------------------------------|

| ADE-LIM  | Alternating Direction Explicit Latency Insertion Method |

| CDM      | Charged Device Model                                    |

| DLTI     | Discrete Linear Time Invariant System                   |

| ECD      | Electrostatic Discharge                                 |

| FDTD     | Finite Difference Time Domain                           |

| KCL      | Kirchhoff's Current Law                                 |

| KVL      | Kirchhoff's Voltage Law                                 |

| LIM      | Latency Insertion Method                                |

| MNA      | Modifier Nodal Analysis                                 |

| PDN      | Power Distribution Network                              |

| PLIM     | Partitioned Latency Insertion Method                    |

| SPICE    | Simulation Program with Integrated Circuit Emphasis     |

| VinC LIM | Voltage-In-Current Latency Insertion Method             |

# CHAPTER 1

## INTRODUCTION

### 1.1 Motivation

Moore’s Law has been driving the technological advances in the semiconductor industry for nearly half a century. Although the pace of doubling the number of transistors in an integrated circuit (IC) has been slowed down over the last few years, the size of the current chip design has reached a significantly large scale. This, together with the increasing operating frequency, has made the issues of power integrity, signal integrity, and reliability more intense. Therefore, designers are in strong demand of precise simulation and modeling at the early design stage.

The conventional circuit simulator in the industry uses Simulation Program with Integrated Circuit Emphasis (SPICE) [1]. SPICE uses the modified nodal analysis (MNA) to solve a set of linear equations that represent the circuit. Because the MNA involves the construction of a large matrix and the calculation of the matrix inversion, SPICE becomes very inefficient and lengthy to solve the large-scale networks. The industry and academia have been actively seeking a solution to address this, by either improving the existing MNA algorithm or by finding a viable alternative without sacrificing accuracy and reliability.

### 1.2 Background

The latency insertion method (LIM) was first proposed to perform fast transient simulations of large networks [2]. It is similar to Yee’s finite difference time domain (FDTD) algorithm and relies on latency in the network to iteratively solve circuit equations using a leapfrog time-stepping scheme

[3, 4]. Thus, it is a linear time solver and can produce simulation results with complexity proportional to the number of nodes, making it attractive to the simulation of large networks. Over the past few years, dedicated efforts have been given to improve and extend the LIM. LIM has been proved to be able to perform steady-state (DC) analysis of a network [5]. It is also extended to the simulation of the nonlinear device, charged device model (CDM) electrostatic discharge (ESD) [6], and even the thermal behavior of the interconnects [7]. Similar to the FDTD [3], LIM is only conditionally stable and has maximum time step constraints. Variances of the basic LIM have been proposed to alleviate this problem as well. Partitioned LIM (PLIM) builds the stability criteria of partitions of different latencies in the circuit and can perform transient simulations significantly faster than the conventional LIM method [8]. The block-LIM executes the leapfrog algorithm at the block level which is defined as a subcircuit composed of tightly coupled elements and is suitable for the fast simulation of the network including mutual coupling elements [9]. The Alternating Direction Explicit LIM (ADE-LIM) employs the ADE algorithm and is able to circumvent the time step limitation [10]. The voltage-in-current LIM (VinC LIM) reformulates the basic LIM equations and use a forward-branching scheme to overcome the time step size limitation in the basic LIM and can achieve unconditional stability [11]. This thesis will focus on the VinC LIM, especially the analysis of its stability. Mathematical derivation of the stability in a single cell will be given, followed by the real applications.

### 1.3 Outline

The rest of the thesis is organized as follow:

Chapter 2 provides more background information on the latency insertion method. We explain the algorithm formulation of basic LIM and analyze its stability. This includes discussion of restrictions in the basic LIM.

Chapter 3 discusses the newly developed voltage-in-current latency insertion method. It is an advancement of the basic LIM and is supposed to have better stability. We derive the formulation of VinC LIM from the basic LIM. The stability of VinC LIM is extensively elaborated and analyzed. We give a mathematical proof that VinC LIM can overcome the simulation time step

restriction of the basic LIM and greatly improved the simulation speed.

Chapter 4 uses examples to present the applications of VinC LIM to common large networks. The particular circuit we use in this section is the on-chip power distribution network. We simulate the PDN using both basic LIM algorithms and VinC LIM algorithms. The simulation results demonstrate that VinC LIM can maintain stability even when the time step size is larger than the maximum constraints of the basic LIM.

Finally, Chapter 5 concludes this thesis and discusses possible future works.

# CHAPTER 2

## LATENCY INSERTION METHOD

### 2.1 Basic Formulation

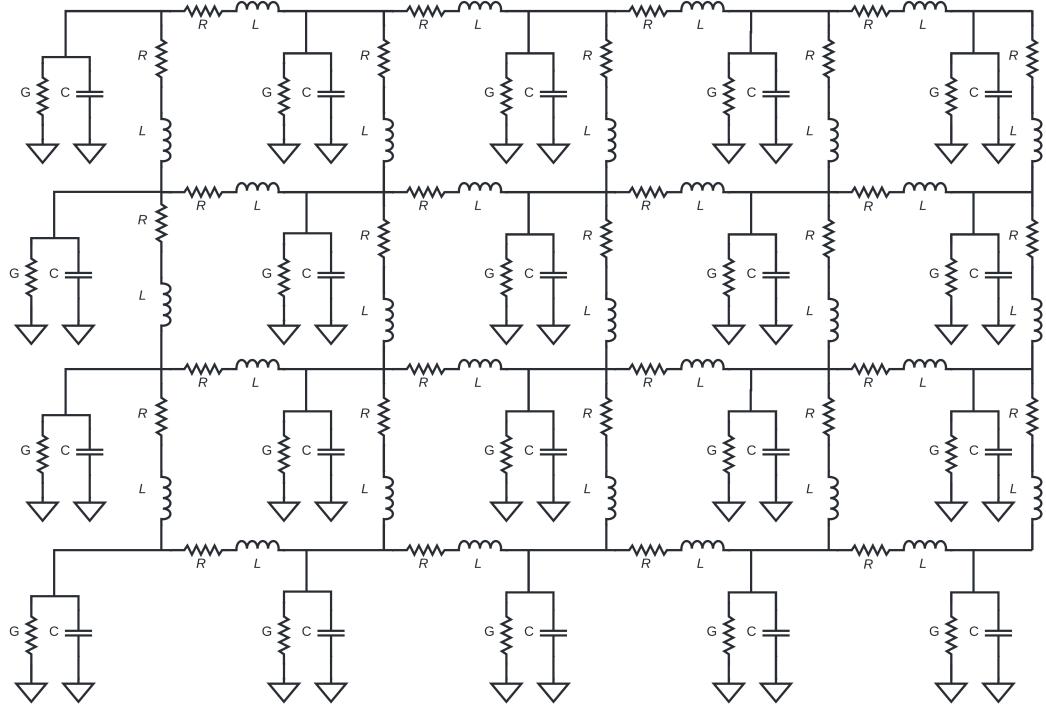

LIM is similar to the FDTD method based on Yee's algorithm [3], but from a circuit perspective. It has linear numerical complexity and can be applied to any arbitrary circuit that can be described as nodes with interconnecting branches. Voltage is defined at every node and current is defined at every branch. Here, we use a grid of RLGC (Figure 2.1) circuits to explain the formulations of LIM because in the high-frequency domain, any arbitrary interconnect can be represented by this general topology, after combinations of Thévenin and Norton transformations.

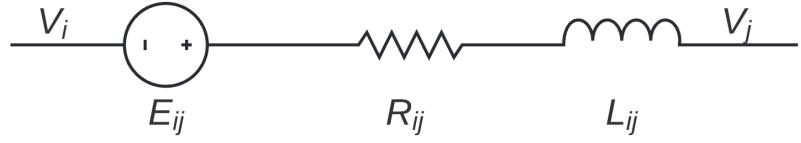

In this topology, each branch can be represented by a series combination of a voltage source, a resistor and an inductor, as shown in Figure 2.2. Applying Kirchhoff's voltage law (KVL), we can get

$$V_i - V_j = L_{ij} \left( \frac{\partial I_{ij}}{\partial t} \right) + R_{ij} I_{ij} - E_{ij} \quad (2.1)$$

Substituting the partial derivative with the finite-difference approximation, Equation 2.1 becomes:

$$V_i^{n+\frac{1}{2}} - V_j^{n+\frac{1}{2}} = L_{ij} \left( \frac{I_{ij}^{n+1} - I_{ij}^n}{\Delta t} \right) + R_{ij} I_{ij}^{n+1} - E_{ij}^{n+\frac{1}{2}} \quad (2.2)$$

Solving for the latest branch current yields:

$$I_{ij}^{n+1} = I_{ij}^n + \frac{\Delta t}{L_{ij}} \left( V_i^{n+\frac{1}{2}} - V_j^{n+\frac{1}{2}} - R_{ij} I_{ij}^{n+1} - E_{ij}^{n+\frac{1}{2}} \right) \quad (2.3)$$

Note that same as the FDTD method, the voltages are computed at half time steps while the currents are computed at full time steps [12].

Figure 2.1: RLGC grid.

Figure 2.2: LIM branch topology.

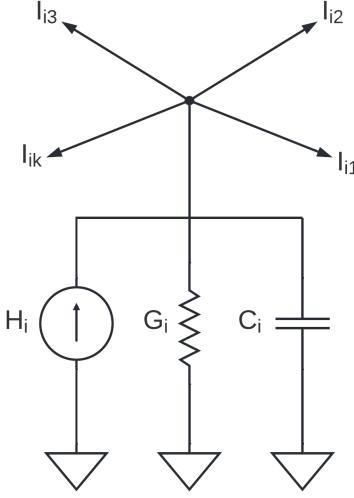

Each node can be represented by a parallel combination of a current source, a conductance, and a capacitor to ground, as shown in Figure 2.3.  $k$  branches are connected to node  $i$ . Applying Kirchhoff's current law (KCL) at node  $i$ , we can get:

$$C_i \left( \frac{\partial V}{\partial t} \right) + G_i V_i - H_i = - \sum_{k=1}^{M_i} I_{ik}^n \quad (2.4)$$

Again, substituting the partial derivative with the finite-difference approximation, Equation 2.1 becomes:

$$C_i \left( \frac{V_i^{n+\frac{1}{2}} - V_i^{n-\frac{1}{2}}}{\Delta t} \right) + G_i V_i^{n-\frac{1}{2}} - H_i^n = - \sum_{k=1}^{M_i} I_{ik}^n \quad (2.5)$$

Figure 2.3: LIM node topology.

Solving for the latest node voltage yields:

$$V_i^{n+\frac{1}{2}} = V_i^{n-\frac{1}{2}} + \frac{\Delta t}{C_i} \left( - \sum_{k=1}^{M_i} I_{ik}^n - G_i V_i^{n-\frac{1}{2}} + H_i^n \right) \quad (2.6)$$

Equation 2.3 and Equation 2.6 give us the update formulations for branch currents and node voltages, which have half a time step offset. Thus we can alternately use them to update branch currents and node voltages in a leapfrog manner. As the derivation indicates, a latency generated by reactive components ( $L_{ij}$  and  $C_i$ ) needs to be presented at each node and in each branch to use LIM. If it is not, a small fictitious inductor needs to be inserted in each branch and a small fictitious capacitor needs to be inserted at each node.

Equation 2.2 and Equation 2.5 are so-called fully explicit formulations. LIM have two various formulations: implicit and semi-implicit. To get the implicit formulations, we replace the term  $R_{ij}I_{ij}^n$  in Equation 2.2 and  $G_iV_i^{n-\frac{1}{2}}$  in Equation 2.5 with  $R_{ij}I_{ij}^{n+1}$  and  $G_iV_i^{n+\frac{1}{2}}$ . Now the update formulations for branch currents and node voltages become:

$$I_{ij}^{n+1} = \left( \frac{L_{ij}}{\Delta t} + R_{ij} \right)^{-1} \cdot \left( \frac{L_{ij}}{\Delta t} I_{ij}^n + V_i^{n+\frac{1}{2}} - V_j^{n+\frac{1}{2}} + E_{ij}^{n+\frac{1}{2}} \right) \quad (2.7)$$

$$V_i^{n+\frac{1}{2}} = \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \cdot \left( \frac{C_i}{\Delta t} V_i^{n-\frac{1}{2}} - \sum_{k=1}^{M_i} I_{ik}^n + H_i^n \right) \quad (2.8)$$

To get the semi-implicit formulations, we replace the term  $R_{ij}I_{ij}^n$  in Equation 2.2 and  $G_iV_i^{n-\frac{1}{2}}$  in Equation 2.5 with  $\frac{R_{ij}(I_{ij}^{n+1}+I_{ij}^n)}{2}$  and  $\frac{G_i(V_i^{n+\frac{1}{2}}+V_i^{n-\frac{1}{2}})}{2}$ . Now the update formulations for branch currents and node voltages become:

$$I_{ij}^{n+1} = \left( \frac{L_{ij}}{\Delta t} + \frac{R_{ij}}{2} \right)^{-1} \cdot \left( \left( \frac{L_{ij}}{\Delta t} - \frac{R_{il}}{2} \right) I_{ij}^n + V_i^{n+\frac{1}{2}} - V_j^{n+\frac{1}{2}} + E_{ij}^{n+\frac{1}{2}} \right) \quad (2.9)$$

$$V_i^{n+\frac{1}{2}} = \left( \frac{C_i}{\Delta t} + \frac{G_i}{2} \right)^{-1} \cdot \left( \left( \frac{C_i}{\Delta t} + \frac{G_i}{2} \right) V_i^{n-\frac{1}{2}} - \sum_{k=1}^{M_i} I_{ik}^n + H_i^n \right) \quad (2.10)$$

## 2.2 Stability of LIM

Similar to the FDTD algorithm, LIM is only conditionally stable [3]. To facilitate the evaluation of stability, we use the vector-matrix form of the LIM formulations. We rewrite 2.5 and 2.2 into semi-implicit formulations:

$$C_i \left( \frac{V_i^{n+\frac{1}{2}} - V_i^{n-\frac{1}{2}}}{\Delta t} \right) + G_i \left( \frac{V_i^{n+\frac{1}{2}} + V_i^{n-\frac{1}{2}}}{2} \right) - H_i^n = - \sum_{k=1}^{M_i} I_{ik}^n \quad (2.11)$$

$$V_i^{n+\frac{1}{2}} - V_j^{n+\frac{1}{2}} = L_{ij} \left( \frac{I_{ij}^{n+1} - I_{ij}^n}{\Delta t} \right) + R_{ij} \left( \frac{I_{ij}^{n+1} + I_{ij}^n}{2} \right) - E_{ij}^{n+\frac{1}{2}} \quad (2.12)$$

Equation 2.11 can then be written in the vector-matrix form:

$$\mathbf{C} \left( \frac{\mathbf{v}^{n+\frac{1}{2}} - \mathbf{v}^{n-\frac{1}{2}}}{\Delta t} \right) + \mathbf{G} \left( \frac{\mathbf{v}^{n+\frac{1}{2}} + \mathbf{v}^{n-\frac{1}{2}}}{2} \right) - \mathbf{h}^n = -\mathbf{M}\mathbf{i}^n \quad (2.13)$$

where  $\mathbf{v}$  is the node voltage vector of dimension  $N_n$  ( $N_n$  is the total number of nodes),  $\mathbf{i}$  is the branch current vector of dimension  $N_b$  ( $N_b$  is the total number of branches),  $\mathbf{C}$  and  $\mathbf{G}$  are diagonal matrices of dimensions  $N_n \times N_n$ , with the values of the capacitance and conductance at each node on the main diagonal,  $\mathbf{h}$  is a vector of dimension  $N_n$  containing all the current sources at each node; and  $\mathbf{M}$  is the incidence matrix of dimensions  $N_n \times N_b$ .

The following is the definition of  $\mathbf{M}$ :

- $\mathbf{M}_{qp} = \mathbf{1}$  if branch  $p$  is incident at node  $q$  and the current flows away from node  $q$ .

- $\mathbf{M}_{qp} = -\mathbf{1}$  if branch  $p$  is incident at node  $q$  and the current flows into node  $q$ .

- $\mathbf{M}_{qp} = \mathbf{0}$  if branch  $p$  is not incident at node  $q$ .

From Equation 2.13, we can get the updated formulation for node voltages in the vector-matrix form:

$$\mathbf{v}^{n+\frac{1}{2}} = \left( \frac{\mathbf{C}}{\Delta t} + \frac{\mathbf{G}}{2} \right)^{-1} \left[ \left( \frac{\mathbf{C}}{\Delta t} - \frac{\mathbf{G}}{2} \right) \mathbf{v}^{n-\frac{1}{2}} + \mathbf{h}^n - \mathbf{M}\mathbf{i}^n \right] \quad (2.14)$$

Similarly, Equation 2.12 can then be written in the vector-matrix form:

$$\mathbf{M}^T \mathbf{v}^{n+\frac{1}{2}} = \frac{\mathbf{L}}{\Delta t} (\mathbf{i}^{n+1} - \mathbf{i}^n) + \frac{\mathbf{R}}{2} (\mathbf{i}^{n+1} + \mathbf{i}^n) - \mathbf{e}^{n+\frac{1}{2}} \quad (2.15)$$

Solving the updated formulation for branch currents in the vector-matrix form yields:

$$\mathbf{i}^{n+1} = \left( \frac{\mathbf{L}}{\Delta t} + \frac{\mathbf{R}}{2} \right)^{-1} \left[ \left( \frac{\mathbf{L}}{\Delta t} - \frac{\mathbf{R}}{2} \right) \mathbf{i}^n + \mathbf{e}^{n+\frac{1}{2}} + \mathbf{M}^T \mathbf{v}^{n+\frac{1}{2}} \right] \quad (2.16)$$

where  $\mathbf{L}$  and  $\mathbf{R}$  are diagonal matrices of dimensions  $N_b \times N_b$ , with the values of the inductance and resistance in each branch on the main diagonal, and  $\mathbf{e}$  is a vector of dimension  $N_b$  containing all the voltage sources in each node.

Now let's make the following definitions to simplify the formulations:

$$\mathbf{P}_+ = \left( \frac{\mathbf{C}}{\Delta t} + \frac{\mathbf{G}}{2} \right)^{-1} \quad \mathbf{P}_- = \left( \frac{\mathbf{C}}{\Delta t} - \frac{\mathbf{G}}{2} \right) \quad (2.17)$$

$$\mathbf{Q}_+ = \left( \frac{\mathbf{L}}{\Delta t} + \frac{\mathbf{R}}{2} \right)^{-1} \quad \mathbf{Q}_- = \left( \frac{\mathbf{L}}{\Delta t} - \frac{\mathbf{R}}{2} \right) \quad (2.18)$$

Equation 2.14 and Equation 2.16 can then be rewritten into:

$$\mathbf{v}^{n+\frac{1}{2}} = \mathbf{P}_+ \mathbf{P}_- \mathbf{v}^{n-\frac{1}{2}} - \mathbf{P}_+ \mathbf{M} \mathbf{i}^n + \mathbf{P}_+ \mathbf{h}^n \quad (2.19)$$

$$\mathbf{i}^{n+1} = \mathbf{Q}_+ \mathbf{Q}_- \mathbf{i}^n + \mathbf{Q}_+ \mathbf{M}^T \mathbf{v}^{n+\frac{1}{2}} + \mathbf{Q}_+ \mathbf{e}^{n+\frac{1}{2}} \quad (2.20)$$

Substituting Equation 2.19 into Equation 2.20 yields:

$$\begin{aligned} \mathbf{i}^{n+1} = & \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \mathbf{P}_- \mathbf{v}^{n-\frac{1}{2}} + (\mathbf{Q}_+ \mathbf{Q}_- - \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \mathbf{M}) \mathbf{i}^n \\ & + \mathbf{Q}_+ \mathbf{e}^{n+\frac{1}{2}} + \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \mathbf{h}^n \end{aligned} \quad (2.21)$$

We can group Equation 2.19 and Equation 2.21 into a discrete linear time invariant system (DLTI) representation:

$$\begin{bmatrix} \mathbf{v}^{n+1/2} \\ \mathbf{i}^{n+1} \end{bmatrix} = \begin{bmatrix} \mathbf{P}_+ \mathbf{P}_- & -\mathbf{P}_+ \mathbf{M} \\ \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \mathbf{P}_- & \mathbf{Q}_+ \mathbf{Q}_- - \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \mathbf{M} \end{bmatrix} \begin{bmatrix} \mathbf{v}^{n-1/2} \\ \mathbf{i}^n \end{bmatrix} + \begin{bmatrix} 0 & \mathbf{P}_+ \\ \mathbf{Q}_+ & \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \end{bmatrix} \begin{bmatrix} \mathbf{e}^{n+1/2} \\ \mathbf{h}^n \end{bmatrix} \quad (2.22)$$

For a DLTI to be asymptotically stable, all the eigenvalues of

$$\mathbf{A} = \begin{bmatrix} \mathbf{P}_+ \mathbf{P}_- & -\mathbf{P}_+ \mathbf{M} \\ \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \mathbf{P}_- & \mathbf{Q}_+ \mathbf{Q}_- - \mathbf{Q}_+ \mathbf{M}^T \mathbf{P}_+ \mathbf{M} \end{bmatrix} \quad (2.23)$$

should have magnitude strictly less than one.  $\mathbf{A}$  is called the amplification matrix and can be used to determine the maximum time step  $\Delta t$  that makes the system stable [13].

Using the amplification matrix, we can computer the exact upper bound on the time step of the basic LIM simulation. However, calculating the eigenvalues of the amplification matrix every time is usually tedious and complicated. An alternative way is to use the direct Lyapunov method [14], where the upper bound of  $\Delta t$  is given by:

$$\Delta t < \sqrt{2} \min_{i=1}^{N_n} \left( \sqrt{\frac{C_i}{N_b^i} \min_{p=1}^{N_b^i} L_{i,p}} \right) \quad (2.24)$$

where  $N_n$  is the total number of nodes of the system,  $N_b$  is the total number of branches of the system,  $C_i$  is the shunt capacitance at node  $i$ ;  $N_b^i$  is the number of branches connected to node  $i$ ; and  $L_{i,p}^p$  is the value of  $p$ th series inductor connected to node  $i$ . In case that no more than two branches are connected at each node, Equation 2.24 can be further simplified to [15]:

$$\Delta t < \min_{i=1}^{N_b} \left( \sqrt{L_i \min(C_i, C_{i+1})} \right) \quad (2.25)$$

## 2.3 Summary

In this chapter, we present the formulations of the basic LIM and discuss its stability condition. It is illustrated that LIM has linear numerical complexity by utilizing the latency of a circuit, and is a viable alternative to the conventional SPICE to simulate large networks. However, basic LIM is only conditional stable and complex calculations need to be done to determine the maximum time step of the simulation. This can hurt the simulation speed. Especially when we need to insert fictitious latency into the circuit, the time step is bounded by the small fictitious values and limiting our simulation speed.

# CHAPTER 3

## VOLTAGE-IN-CURRENT LATENCY INSERTION METHOD

From Section 2.2, we know that the basic LIM algorithm is only conditionally stable and an expensive computation must be done to calculate the maximum time step  $\Delta t$ , by solving either the eigenvalues of the amplification matrix or the direct Lyapunov method (also known as the energy method) [14]. To overcome the time step size limitation in the basic LIM, researchers have proposed an improved LIM formulation: voltage-in-current latency insertion method [11].

### 3.1 Formulation

To get the formulations of the VinC LIM, we reformulate Equation 2.7 and Equation 2.8 into implicit formulations at the same time step of  $t = n + 1$ :

$$V_i^{n+1} = \left( G_i + \frac{C_i}{\Delta t} \right)^{-1} \left( \frac{C_i}{\Delta t} V_i^n - \sum_{k=1}^{M_i} I_{ik}^{n+1} + H_i^{n+1} \right) \quad (3.1)$$

$$I_{ij}^{n+1} = \left( R_{ij} + \frac{L_{ij}}{\Delta t} \right)^{-1} \left( \frac{L_{ij}}{\Delta t} I_{ij}^n + V_i^{n+1} - V_j^{n+1} + E_{ij}^{n+1} \right) \quad (3.2)$$

Substituting the voltage in Equation 3.1 into Equation 3.2 yields:

$$I_{ij}^{n+1} = \frac{\frac{L_{ij} I_{ij}^n}{\Delta t} + \frac{\frac{C_i}{\Delta t} V_i^n - \sum_{k=1}^{M_i} I_{ik}^{n+1} + H_i^{n+1}}{G_i + \frac{C_i}{\Delta t}} - \frac{\frac{C_j}{\Delta t} V_j^n - \sum_{k=1}^{M_j} I_{jk}^{n+1} + H_j^{n+1}}{G_j + \frac{C_j}{\Delta t}} + E_{ij}^{n+1}}{R_{ij} + \frac{L_{ij}}{\Delta t}} \quad (3.3)$$

Then rearrange it by pulling out all the  $I_{ij}^{n+1}$  moving to the left hand side:

$$I_{ij}^{n+1} = \frac{\frac{L_{ij}}{\Delta t} I_{ij}^n + \frac{C_i}{\Delta t} V_i^n - \sum_{k=1, k \neq j}^{M_i} I_{ik}^{n+p} + H_i^{n+1}}{G_i + \frac{C_i}{\Delta t}} - \frac{\frac{C_j}{\Delta t} V_j^n - \sum_{k=1, k \neq j}^{M_j} I_{jk}^{n+p} + H_j^{n+1}}{G_j + \frac{C_j}{\Delta t}} + E_{ij}^{n+1} \quad (3.4)$$

where  $\sum_{k=1, k \neq j}^{M_i} I_{ik}^{n+p}$  adds all the branch currents flowing away from node  $i$ , and  $\sum_{k=1, k \neq i}^{M_j} I_{jk}^{n+p}$  adds all the branch currents flowing away from node  $j$ , without including the  $I_{ij}$  current in both summations. In order to circumvent the added complexity that is introduced in the implicit formulation, a forward branch-marching scheme is applied here. We have  $p = 0$  if the associate current for that branch has not been solved for before the present iteration, whereas  $p = 1$  if the associate current for that branch has been solved for before the present iteration.

Equation 3.4 gives us the update formulations for branch currents in VinC LIM. Once we update the current, we can use Equation 3.1 to update the voltage.

## 3.2 Stability of VinC LIM

Compared to the basic LIM formulations, the VinC LIM formulations are supposed to reach unconditionally stability. There are many experiments demonstrating that VinC LIM significantly improves the stability and allows the use of time steps much larger than that is permitted in the basic LIM, which effectively reduces the simulation time. However, no mathematical proof has been given to illustrate the stability of VinC LIM formulations. Therefore, in this section, we will show that VinC LIM is unconditionally stable in mathematics.

Since LIM relies on the latency generated by the passive devices in the circuit to perform simulation, all the circuits can be seen as consisting of basic RLGC cells from the perspective of LIM, after any necessary fictitious inductors or capacitors are inserted. Thus, We want to prove that VinC LIM has unconditional stability in the case of single-cell circuit. Consider the single-cell circuit shown in Figure 3.1. This circuit has one branch and one node. Consequently, the incidence matrix for this circuit is  $M = 1$ .

Figure 3.1: Single-cell circuit.

Equation 3.1 and Equation 3.4 now become:

$$V_i^{n+1} = \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \left( \frac{C_i}{\Delta t} V_i^n - I_{ij}^{n+1} \right) \quad (3.5)$$

$$I_{ij}^{n+1} = \frac{\frac{L_{ij}}{\Delta t} I_{ij}^n + \frac{C_i}{\Delta t} V_i^n}{R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1}} \quad (3.6)$$

Substituting the updated branch current from Equation 3.6 to Equation 3.5 yields:

$$V_i^{n+1} = \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \left( \frac{C_i}{\Delta t} V_i^n - \frac{\frac{L_{ij}}{\Delta t} I_{ij}^n + \frac{C_i}{\Delta t} V_i^n}{R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1}} \right) \quad (3.7)$$

Rearranging the terms of  $V_i^n$  and  $I_{ij}^n$  respectively yields:

$$\begin{aligned} V_i^{n+1} &= \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \left[ \frac{C_i}{\Delta t} - \frac{\frac{C_i}{\Delta t}}{\left( G_i + \frac{C_i}{\Delta t} \right) \left( R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \right)} \right] V_i^n \\ &\quad - \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \left[ \frac{\frac{L_{ij}}{\Delta t}}{R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1}} \right] I_{ij}^n \end{aligned} \quad (3.8)$$

Equation 3.8 and Equation 3.6 can then be grouped together to obtain a DLTI representation:

$$\begin{bmatrix} V_i^{n+1} \\ I_{ij}^{n+1} \end{bmatrix} = \mathbf{A} \begin{bmatrix} V_i^n \\ I_{ij}^n \end{bmatrix} \quad (3.9)$$

It is clear that the amplification matrix in a single-cell condition is

$$\mathbf{A} = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \quad (3.10)$$

where

$$\begin{aligned} A_{11} &= \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \left[ \frac{C_i}{\Delta t} - \frac{\frac{C_i}{\Delta t}}{\left( G_i + \frac{C_i}{\Delta t} \right) \left( R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \right)} \right] \\ A_{12} &= - \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \left[ \frac{\frac{L_{ij}}{\Delta t}}{R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1}} \right] \\ A_{21} &= \frac{\frac{C_i}{\Delta t}}{\left( G_i + \frac{C_i}{\Delta t} \right) \left( R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1} \right)} \\ A_{22} &= \frac{\frac{L_{ij}}{\Delta t}}{R_{ij} + \frac{L_{ij}}{\Delta t} + \left( \frac{C_i}{\Delta t} + G_i \right)^{-1}} \end{aligned} \quad (3.11)$$

In order to simplify the notation, we make the following definitions:

$$h = \Delta t, \quad K = \frac{1}{L}, \quad Y = \frac{1}{C + hG} \quad (3.12)$$

The submatrices for this single-cell circuit are scalars and can be rewritten as follows:

$$A_{11} = \frac{CY + RKhCY}{1 + RKh + Kh^2Y} \quad A_{12} = \frac{-Yh}{1 + RKh + Kh^2Y} \quad (3.13)$$

$$A_{21} = \frac{CYKh}{1 + RKh + Kh^2Y} \quad A_{22} = \frac{1}{1 + RKh + Kh^2Y}$$

The amplification matrix can then be rewritten as

$$\mathbf{A} = \begin{bmatrix} \frac{CY + RKhCY}{1 + RKh + Kh^2Y} & \frac{-Yh}{1 + RKh + Kh^2Y} \\ \frac{CYKh}{1 + RKh + Kh^2Y} & \frac{1}{1 + RKh + Kh^2Y} \end{bmatrix} \quad (3.14)$$

To check the stability condition of the VinC LIM, we must compute the eigenvalues of  $\mathbf{A}$

$$|\mathbf{A} - \lambda \mathbf{I}| = \begin{vmatrix} \frac{CY + RKhCY}{1 + RKh + Kh^2Y} - \lambda & \frac{-Yh}{1 + RKh + Kh^2Y} \\ \frac{CYKh}{1 + RKh + Kh^2Y} & \frac{1}{1 + RKh + Kh^2Y} - \lambda \end{vmatrix} = 0 \quad (3.15)$$

Arranging the terms for different orders of  $\lambda$  yields:

$$\begin{aligned} & (1 + RKh + Kh^2Y)^2 \lambda^2 - (CY + RKhCY + 1) (1 + RKh + Kh^2Y) \lambda \\ & + CY + RKhCY + CY^2Kh^2 = 0 \end{aligned} \quad (3.16)$$

If we assume  $G = 0$ , then

$$Y = \frac{1}{C} \rightarrow CY = 1 \quad (3.17)$$

$$KY = \frac{1}{LC} = u \quad (3.18)$$

Substituting Equation 3.17 and Equation 3.18 into Equation 3.16 yields:

$$\begin{aligned} & (1 + RKh + h^2u)^2 \lambda^2 - (2 + RKh) (1 + RKh + h^2u) \lambda \\ & + (h^2u + RKh + 1) = 0 \end{aligned} \quad (3.19)$$

Now let's solve for  $\lambda$ :

$$\begin{aligned} \lambda &= \frac{(2 + RKh) (1 + RKh + h^2u) \pm \sqrt{(1 + RKh + h^2u)^2 (h^2R^2K^2 - 4h^2u)}}{2 (1 + RKh + h^2u)^2} \\ &= \frac{2 + RKh}{2 (1 + RKh + h^2u)} \pm \frac{\sqrt{h^2R^2K^2 - 4h^2u}}{2 (1 + RKh + h^2u)} \end{aligned} \quad (3.20)$$

Since the  $\lambda$  contains a square root expression, we have to think about two cases: the positive square root of  $\sqrt{h^2R^2K^2 - 4h^2u}$  and the negative square root of  $\sqrt{h^2R^2K^2 - 4h^2u}$ .

### 3.2.1 Case A

Let us now assume that the term within the radical of Equation 3.20 is less than 0, we can rewrite  $\lambda$  as:

$$\lambda = \frac{2 + RKh}{2(1 + RKh + h^2u)} \pm j \frac{\sqrt{4h^2u - h^2R^2K^2}}{2(1 + RKh + h^2u)} \quad (3.21)$$

This condition is satisfied if

$$h^2u - h^2R^2K^2 > 0 \quad (3.22)$$

$$R^2C < 4L \quad (3.23)$$

The magnitude of  $\lambda$  is obtained through:

$$\begin{aligned} |\lambda|^2 &= \left[ \frac{2 + RKh}{2(1 + RKh + h^2u)} \right]^2 + \frac{4h^2u - h^2R^2K^2}{4(1 + RKh + h^2u)^2} \\ &= \frac{4 + 4RKh + 4h^2u}{4(1 + RKh + h^2u)^2} \end{aligned} \quad (3.24)$$

Now let's solve for  $\lambda$ :

$$\begin{aligned} |\lambda| &= \frac{\sqrt{1 + RKh + h^2u}}{(1 + RKh + h^2u)} \\ &= \frac{1}{\sqrt{1 + RKh + h^2u}} \end{aligned} \quad (3.25)$$

It is clear from Equation 3.25 that  $\lambda$  is always smaller than 1, which indicates the cell is unconditional stable in this case.

### 3.2.2 Case B

Let us now assume that the term within the radical of 3.20 is equal or greater than 0, This condition is satisfied if:

$$h^2R^2K^2 - 4h^2u > 0 \quad (3.26)$$

Then the magnitude of the eigenvalues of the amplification matrix can be expressed by:

$$|\lambda|^2 = \left[ \frac{2 + RKh}{2(1 + RKh + h^2u)} \pm \frac{\sqrt{h^2R^2k^2 - 4h^2u}}{2(1 + RKh + h^2u)} \right]^2 \quad (3.27)$$

Rearranging the terms yields the following equation:

$$|\lambda|^2 = \left[ 1 - \frac{RKh + 2h^2u}{2(1 + RKh + h^2u)} \pm \frac{\sqrt{h^2R^2k^2 - 4h^2u}}{2(1 + RKh + h^2u)} \right]^2 \quad (3.28)$$

$\lambda$  can have two magnitudes here:

$$\lambda_1 = \left| 1 - \frac{RKh + 2h^2u}{2(1 + RKh + h^2u)} - \frac{\sqrt{h^2R^2k^2 - 4h^2u}}{2(1 + RKh + h^2u)} \right| \quad (3.29)$$

$$\lambda_2 = \left| 1 - \frac{RKh + 2h^2u}{2(1 + RKh + h^2u)} + \frac{\sqrt{h^2R^2k^2 - 4h^2u}}{2(1 + RKh + h^2u)} \right| \quad (3.30)$$

Let's take a look at Equation 3.29 first. It is clear to see that

$$2(1 + RKh + h^2u) > RKh + 2h^2u > \sqrt{h^2R^2k^2 - 4h^2u} > 0 \quad (3.31)$$

Substituting Equation 3.31 into Equation 3.29 gives us:

$$\left| \frac{2(1 + RKh + h^2u)}{2(1 + RKh + h^2u)} - \frac{RKh + 2h^2u}{2(1 + RKh + h^2u)} - \frac{\sqrt{h^2R^2k^2 - 4h^2u}}{2(1 + RKh + h^2u)} \right| < 1 \quad (3.32)$$

Now, let's take a look at Equation 3.30. Based on Equation 3.31 We can see:

$$2(1 + RKh + h^2u) + \sqrt{h^2R^2k^2 - 4h^2u} < 2(1 + RKh + h^2u) + RKh + 2h^2u \quad (3.33)$$

$$2(1 + RKh + h^2u) - RKh + 2h^2u + \sqrt{h^2R^2k^2 - 4h^2u} < 2(1 + RKh + h^2u) \quad (3.34)$$

Substituting Equation 3.34 into Equation 3.30 gives us:

$$\lambda_2 = \left| 1 - \frac{RKh + 2h^2u}{2(1 + RKh + h^2u)} + \frac{\sqrt{h^2R^2k^2 - 4h^2u}}{2(1 + RKh + h^2u)} \right| < 1 \quad (3.35)$$

Both magnitudes of  $\lambda$  are strictly smaller than 1 and give us unconditional

stability in this case. This, together with 3.2.1 proves that VinC LIM is unconditional stable in a single-cell circuit.

### 3.3 Summary

In this chapter, we derive the formulations of the VinC LIM from the basic LIM. The stability of VinC LIM is thoroughly analyzed and discussed with a solid mathematical proof. VinC LIM inherits all the benefits of basic LIM, such as linear numerical complexity. Moreover, it overcomes the time step constrains the basic LIM has. By leveraging the larger time step, the simulation can be finished in a much shorter time while remains unconditionally stable.

# CHAPTER 4

## APPLICATIONS

In previous chapters, we have demonstrated that VinC LIM can achieve unconditional stability as opposed to the basic LIM, theoretically. In this chapter, we want to present the applications of VinC LIM to common large networks and see how it remains its stability in the real-world simulation.

As we've seen from Chapter 2, the formulations and the node/branch structures of LIM are inspired by the discrete distributed model for a transmission line. Thus, one of the most straightforward and suitable applications of the LIM is the transient simulation of a on-chip power distribution network (PDN) as it can be considered as a two-dimensional transmission line and can be well represented by the discrete distributed models [16]. Moreover, an accurate and fast simulation of PDNs at the early design stage is particularly important in the design of modern large scale integrated circuits. Driven by the Moore's Law, the semiconductor industry has fabricated more and more transistors on a single chip. The scaling of chips has requested lower supply voltage due to the power dissipation constrains. The larger number of on-chip transistors, larger interconnect resistance and lower required supply voltage can cause a significant voltage drop (IR drop) on the grid. The momentary fluctuations of voltages can lead to undesired behavior and hurt the reliability and even the functionality of the system. Thus, PDN is an important electrical circuit in modern chip to carry a large amount of supply current and an accurate simulation of the IR drop in the power grid is important to the designers.

### 4.1 Model of the Power Plane

A 3-D diagram of the PDN structure is shown in Figure 4.1. It includes wire resistances, inductances and capacitances, as well as the decoupling ca-

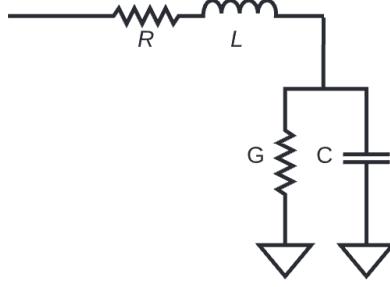

pacitors, VDD pads, and the current sources that represent currents drawn by logic gates or functional blocks [17]. A simplified circuit model of the structure is shown in Figure 4.2. A typical PDN can be simplified as consisting of a conducting power plane separated from a conducting ground plane by a dielectric. Being able to simulate the power planes efficiently and accurately is critical to addressing the power integrity and signal integrity issues of the PDN. The plane structure and the equivalent circuit model of a unit cell are shown in Figure 4.3 [18]. The unit cells are arranged in a grid, with each branch containing an inductor and each node containing a capacitor. Thus, it is ideal for usage with LIM because we don't need to insert fictitious passive components to generate latency.

The capacitance and inductance of the unit cell are given in the following equations:

$$C = \epsilon_0 \epsilon_r \frac{w^2}{d} \quad (4.1)$$

$$L = \mu_0 d \quad (4.2)$$

The conductance and resistance are calculated by the following expressions, respectively.

$$G = \omega C \tan \delta \quad (4.3)$$

$$R = \frac{1}{\sigma t} \quad (4.4)$$

Here,  $\epsilon_0 \epsilon_r$  is the permittivity of dielectric;  $w$  is the width of a unit cell;  $d$  is the distance between two planes;  $\mu_0$  is the permittivity of free space;  $\omega$  is the radian frequency;  $\tan \delta$  is the loss tangent;  $t$  is the thickness of the conductor and  $\sigma$  is the conductivity of the conductor. The power plane can be viewed as consisting of such basic RLGC unit cells. The rule of thumb is to have equal to or greater than 20 cells per wavelength in the granularity of the structure. Increasing the number of cells per wavelength can decrease the numerical dispersion error [12].

## 4.2 Simulation Results

To compare the stability of basic LIM and VinC LIM, we simulate the

Figure 4.1: Diagram of the on-chip power distribution network.

power plane using both algorithms. The model we used to conduct the simulation is shown in Figure 4.4. It is a rectangular mesh network that consists of 20 nodes in each dimension. A input current pulse with rise and fall time of 2 ns and pulse width of 5 ns is applied at Node 1. We plot the waveform of the voltage measured at the last node simulated using different time steps.

Figure 4.5, Figure 4.6, and Figure 4.7 show the voltage waveform results at the output node simulated with the basic LIM algorithms. As you can see, the basic LIM is only conditionally stable and starts to oscillate when the time step is 58 ns. This is also the maximum time step size we calculate using the energy method. When the time step size is greater than the limitation, the waveform becomes unstable and doesn't convey meaningful information anymore.

Figure 4.8, Figure 4.9, Figure 4.10, and Figure 4.11 show the voltage waveform results at the output node simulated with the improved VinC LIM algorithms. It is observed from Figure 4.9 that VinC LIM is able to maintain the stability even when the time step size goes beyond the limitation of the basic

Figure 4.2: Circuit model of the on-chip power distribution network.

LIM using the direct Lyapunov method, which is  $\Delta t = 58 \text{ ns}$ . Figure 4.10 and Figure 4.11 show the simulation results with the time step size larger than the limitation of the basic LIM. It is demonstrated that VinC LIM is still stable. Having a large time step size allows us to speed up the simulation when simulating such a large network. However, we can not simply increase the time step size as it can sacrifice the accuracy, as shown in Figure 4.11. Finding the balance point between speed and accuracy is a critical tradeoff we need to make when we want to conduct an efficient and accurate simulation.

Figure 4.3: Plane pair structure and the equivalent circuit of the unit cell.

Figure 4.4: Equivalent circuit model for LIM simulation.

Figure 4.5: Output voltage waveform from basic LIM simulation with  $\Delta t = 5.8 \text{ ns}$ .

Figure 4.6: Output voltage waveform from basic LIM simulation with  $\Delta t = 58 \text{ ns}$ .

Figure 4.7: Output voltage waveform from basic LIM simulation with  $\Delta t = 60 \text{ ns}$ .

Figure 4.8: Output voltage waveform from VinC LIM simulation with  $\Delta t = 5.8 \text{ ns}$ .

Figure 4.9: Output voltage waveform from VinC LIM simulation with  $\Delta t = 58 \text{ ns}$ .

Figure 4.10: Output voltage waveform from VinC LIM simulation with  $\Delta t = 60 \text{ ns}$ .

Figure 4.11: Output voltage waveform from VinC LIM simulation with  $\Delta t = 100 \text{ ns}$ .

# CHAPTER 5

## CONCLUSION AND FUTURE WORK

### 5.1 Conclusion

In this project, an efficient circuit simulation algorithm LIM and its improved version VinC LIM have been discussed. Both of them achieve linear time complexity as opposed to the conventional SPICE and are suitable for the simulation of large networks. Several advancements have been proposed based on the basic LIM and VinC LIM was specifically for overcoming the time step size limitation of the basic LIM. We presented the formulations of the VinC LIM as they derive from the the formulations of the basic LIM. Then we gave a mathematical proof that VinC LIM can achieve unconditional stability in a single-cell circuit.

Next, we present the applications of VinC LIM to the simulations of common large networks. The particular circuit we chose is the power distribute network as it has the desired branch and node structure that make it ideal for the usage of the LIM algorithms. Besides, it is an important circuit component in modern chip design and it requires an efficient and accurate simulation at the early stage to predict the IR drop of the power grid. We simulate the PDN using both basic LIM and VinC LIM to compare their stability. VinC LIM is demonstrate to maintain stability even when the time step size is larger than the constrains of the basic LIM. However, careful attention needs to be paid to choose the appropriate time step size if we want to improve the speed of simulation without sacrificing the accuracy of the simulation.

## 5.2 Future Work

VinC LIM has been demonstrated as an advancement of basic LIM and has both linear time complexity and unconditionally stability. With VinC LIM, we can theoretically simulate the large circuit network using any arbitrary time step size to improve the speed of simulation. However, there are some prospective future work that could be done to further enhance this algorithm.

We have proved that VinC LIM is unconditional stable for passive devices. Further mathematical proof can be done for active devices such as MOSFETs and diodes. The extended formulations for the VinC LIM for the nonlinear devices have been developed [19]. In addition, the formulations for thin-film transistor [20] in the VinC LIM algorithms have been lately presented. Rigid mathematically proof can be done to illustrate that VinC LIM is unconditionally stable theoretically.

Besides, although VinC LIM achieves unconditional stability as compared of basic LIM, the insertion of fictitious inductors and capacitors can not be avoided in some cases. Choosing small latency is critical to the accuracy of the simulation. A particular algorithm can be developed to help find the "small enough" inductance and capacitance.

Another possible future work that can be done is on the tradeoff between performance and accuracy. Though VinC LIM is capable of time step size beyond the limitation of the basic LIM, the time step size can not be too large to maintain the desired accuracy. Finding a time step size that balances both performance and accuracy is necessary in modern chip design as we want to finish the simulation of large network as quick as possible without degrading the accuracy too much. An possible algorithm can be developed to find the "appropriate" time step size for the simulation of large circuit network.

## REFERENCES

- [1] L. W. Nagel, “SPICE2: A computer program to simulate semiconductor circuits,” Ph.D. dissertation, EECS Department, University of California, Berkeley, May 1975. [Online]. Available: <http://www2.eecs.berkeley.edu/Pubs/TechRpts/1975/9602.html>

- [2] J. Schutt-Aine, “Latency insertion method (LIM) for the fast transient simulation of large networks,” *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 48, no. 1, pp. 81–89, 2001.

- [3] K. Yee, “Numerical solution of initial boundary value problems involving maxwell’s equations in isotropic media,” *IEEE Transactions on Antennas and Propagation*, vol. 14, no. 3, pp. 302–307, 1966.

- [4] A. Orlandi and C. Paul, “FDTD analysis of lossy, multiconductor transmission lines terminated in arbitrary loads,” *IEEE Transactions on Electromagnetic Compatibility*, vol. 38, no. 3, pp. 388–399, 1996.

- [5] D. Klokotov and J. Schutt-Aine, “Latency insertion method for the analysis of steady state on-chip power distribution networks and transient simulation of lossy interconnects,” in *2008 Asia-Pacific Microwave Conference*, 2008, pp. 1–4.

- [6] D. Klokotov, “Application of the latency insertion method (LIM) to the analysis of large circuit interconnect networks,” Ph.D. dissertation, University of Illinois at Urbana-Champaign, Champaign, May 2011.

- [7] D. Klokotov and J. E. Schutt-Ainé, “Latency insertion method (LIM) for Electro-Thermal Analysis of 3-D Integrated Systems at Pre-Layout Design Stages, year=2013, volume=3, number=7, pages=1138-1147, doi=10.1109/TCPMT.2012.2232352,” *IEEE Transactions on Components, Packaging and Manufacturing Technology*.

- [8] P. Goh, J. E. Schutt-Ainé, D. Klokotov, J. Tan, P. Liu, W. Dai, and F. Al-Hawari, “Partitioned latency insertion method (PLIM) with stability considerations,” in *2011 IEEE 15th Workshop on Signal Propagation on Interconnects (SPI)*, 2011, pp. 107–110.

- [9] Y. Inoue, T. Sekine, and H. Asai, “Parallel-distributed block-(LIM)-based fast transient simulation of tightly coupled transmission lines,” in *2010 Proceedings 60th Electronic Components and Technology Conference (ECTC)*, 2010, pp. 657–662.

- [10] H. Kurobe, T. Sekine, and H. Asai, “Locally implicit (LIM) for the simulation of PDN modeled by triangular meshes,” *IEEE Microwave and Wireless Components Letters*, vol. 22, no. 6, pp. 291–293, 2012.

- [11] K. Tan, P. Goh, and M. Ain, “Voltage-in-current formulation for the latency insertion method for improved stability,” *Electronics Letters*, vol. 52, pp. 1904–1906, 11 2016.

- [12] *The Finite Difference Method*. John Wiley Sons, Ltd, 2010, ch. 8, pp. 295–341. [Online]. Available: <https://onlinelibrary.wiley.com/doi/abs/10.1002/9780470874257.ch8>

- [13] J. Schutt-Ainé, “Stability analysis for semi-implicit (LIM) algorithm,” in *2009 Asia Pacific Microwave Conference*, 2009, pp. 1270–1272.

- [14] S. Lalgudi, M. Swaminathan, and Y. Kretchmer, “On-chip power-grid simulation using latency insertion method,” *Circuits and Systems I: Regular Papers, IEEE Transactions on*, vol. 55, pp. 914 – 931, 05 2008.

- [15] Z. Deng and J. Schutt-Aine, “Stability analysis of latency insertion method (LIM),” in *Electrical Performance of Electronic Packaging - 2004*, 2004, pp. 167–170.

- [16] M. Swaminathan and A. E. Engin, “Power integrity modeling and design for semiconductors and systems,” 2007.

- [17] S. N. Lalgudi, M. Swaminathan, and Y. Kretchmer, “On-chip power-grid simulation using latency insertion method,” *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 55, no. 3, pp. 914–931, 2008.

- [18] J. Choi, V. Govind, M. Swaminathan, and K. Bharath, “Noise isolation in mixed-signal systems using alternating impedance electromagnetic bandgap (AI-EBG) structure-based power distribution network (PDN),” *IEEE Transactions on Advanced Packaging*, vol. 33, no. 1, pp. 2–12, 2010.

- [19] W. C. Chin, A. Pashkovich, K. Malinauskas, J. E. Schutt-Ainé, H. Ibrahim, N. S. Ahmad, and P. Goh, “Voltage-in-current latency insertion method for diodes and MOSFETs,” *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 10, no. 10, pp. 1708–1720, 2020.

[20] W. C. Chin, A. Pashkovich, J. E. Schutt-Ainé, N. S. Ahmad, and P. Goh, “Thin-film transistor simulations with the voltage-in-current latency insertion method,” *IEEE Access*, vol. 9, pp. 159 334–159 348, 2021.